Stratix gx nios ddr test – Altera High-Speed Development Kit, Stratix GX Edition User Manual

Page 118

7–36

Quartus II Version 3.0

Altera Corporation

Nios Designs

High-Speed Development Kit, Stratix GX Edition User Guide

f

For more information on the software development process, refer to the

Nios literature page on the Altera web site.

Stratix GX Nios DDR Test

This design comprises a Nios processor combined with 2 dual-port

RAMs, a test control state machine, and the Altera DDR Memory

Controller MegaCore function. The design is captured in VHDL and has

a VHDL wrapper to specify the I/O pin names and placements. Because

this is a processor-based test, the actual test consists of running several

object files on the Nios processor and observing the results in a terminal

window on a PC.

The memory tests consist of a series of write, read, and compare cycles.

These cycles write a value to a memory location, read the values back, and

compare the expected value with the value read from the memory. If all

of the values match, the test passes.

f

Refer to “DDR Interface (Stratix GX Nios DDR)” on page 5–22 for

information on how to perform the test.

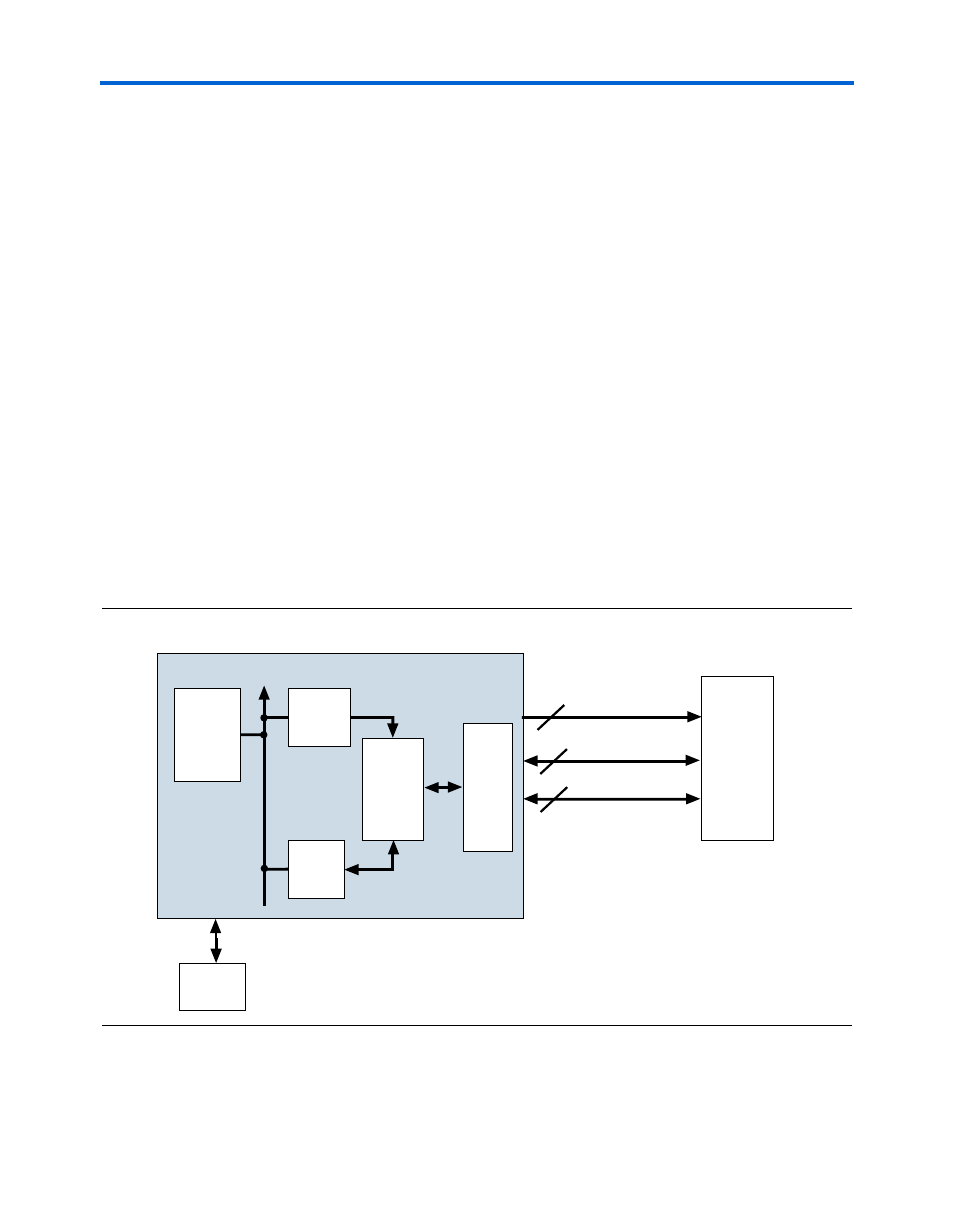

Figure 7–17 shows the Stratix GX Nios DDR logic diagram.

Figure 7–17. Stratix GX Nios DDR Logic Diagram

DDR Data

DDR Status/ Control

DDR Address

13

Add[12:0]

Data[63:0]

63

200-MHz, 128-Mbyte

DDR Card

RS-232

Port

Command

FIFO

Avalon

Bus

Data

RAM

Altera

DDR

IP

Core

30

Stratix GX Device

Nios

CPU

DDR

Test

State

Machine