10-gigabit ethernet mac demonstration, Introduction, Chapter 9. 10-gigabit ethernet mac demonstration – Altera High-Speed Development Kit, Stratix GX Edition User Manual

Page 135: Introduction –1

Altera Corporation

Quartus II Version 3.0

9–1

9. 10-Gigabit Ethernet MAC

Demonstration

Introduction

This demonstration application implements a 10-Gigabit Ethernet MAC

connected to the Stratix GX embedded SERDES device, providing an

XAUI connection to an optional XPAK optical transceiver

module. The demonstration allows you to test the XAUI SERDES

implementation with Ethernet LAN bandwidth.

The demonstration provides the Ethernet MAC with 2-Kbytes of FIFO

buffers per direction, implementing a store-and-forward mechanism to

transfer received frames back to the transmit port. Statistics are collected

on the traffic received. A small, integrated Nios processor accesses these

statistics and presents them on a standard RS-232 terminal. Table 9–1

shows the configuration for the Ethernet MAC core used in the

demomstration.

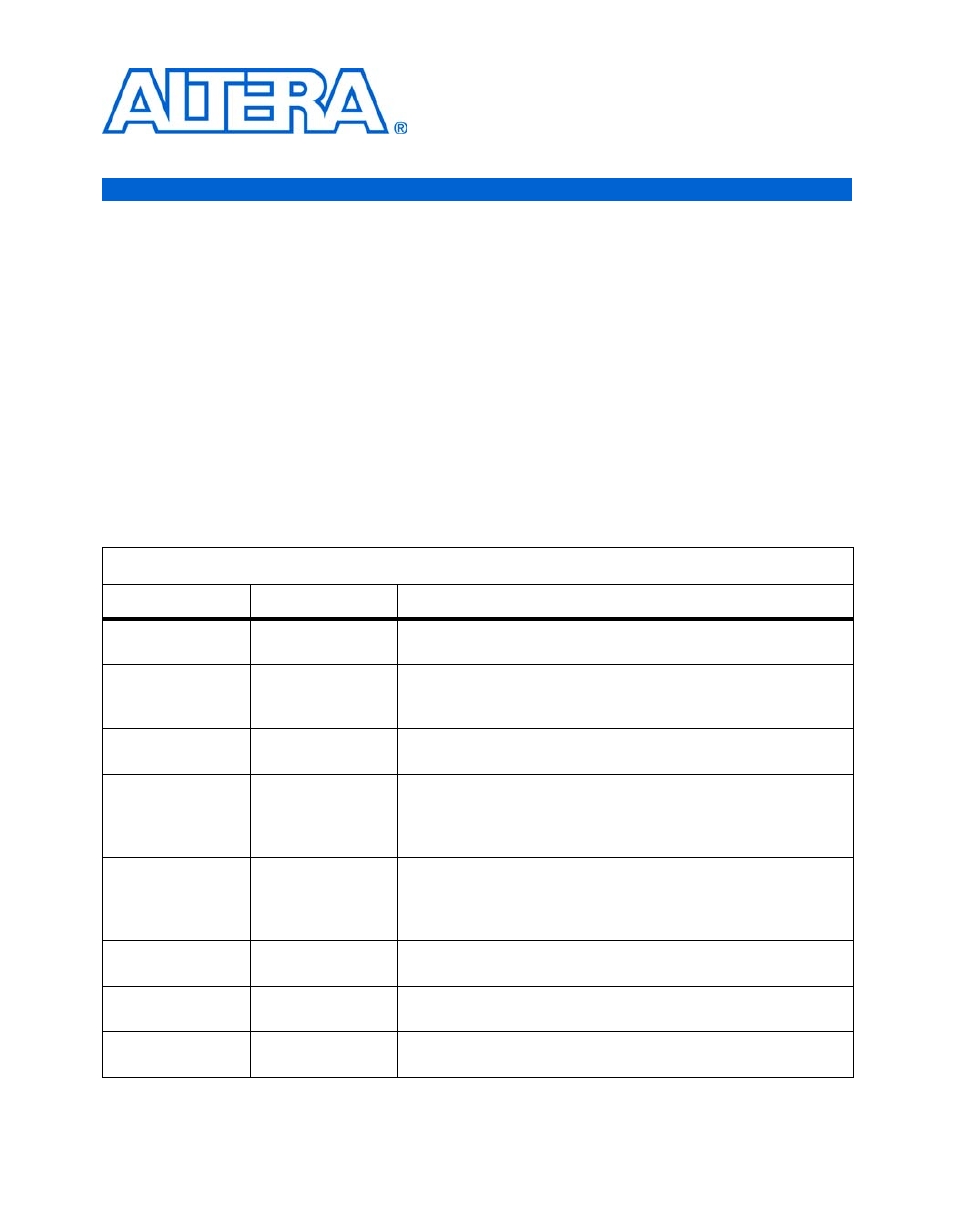

Table 9–1. 10G Ethernet MAC Core Configuration (Part 1 of 2)

Parameter

Setting

Notes

Transmit FIFO

buffer

256 deep x 64 wide

(2 Kbytes)

Can hold standard Ethernet frame.

Transmit FIFO

buffer section

thresholds

0

The TX FIFO buffer is configured in store-and-forward mode.

Transmission begins after a complete frame is available in the

transmit FIFO buffer.

Receive FIFO buffer 256 deep x 64 wide

(2Kbyte)

Can hold complete standard Ethernet frame.

Receive FIFO buffer

section available

32 (256 byte)

The RX FIFO buffer is configured to forward frames to the transmit

FIFO buffer without waiting for end-of-frame if the frame exceeds

256 bytes. If less than 256 byte frames are received, the frame is

forwarded with reception of end-of-frame.

RX FIFO threshold

for automatic pause

frame generation

128 (1024 byte)

As the RX FIFO buffer is programmed in forwarding mode, it usually

will not reach this limit and the MAC operates normally.To force the

receive FIFO buffer to fill up, the transmitter can be put on hold by

generating a pause frame from the Testset.

Pause quanta

32767

If the MAC transmits pause frames, the pause quanta is set to this

value.

MAC address

Disabled

MAC address recognition and insertion is disabled. All frames

received are forwarded unmodified.

CRC remove on

receive

Enabled

The received frame CRC is verified and removed from the frame.