Altera High-Speed Development Kit, Stratix GX Edition User Manual

Page 130

8–2

Quartus II Version 3.0

Altera Corporation

High-Speed Development Kit, Stratix GX Edition User Guide

The demonstration assumes that the Stratix GX development board is

connected through the HM-Zd connector on the source-synchronous side

to a development board from Intel or PMC-Sierra that includes the multi-

channel MAC device. For testing with Intel, you can use the IXD1110

development board with direct interconnect through the reciprocal HM-

Zd connectors. For PMC-Sierra, you can use an interposer card with the

PM2381-KIT development board to bridge the HM-Zd connector to the

Molex 74057-1001 connector used on the PMC-Sierra board.

f

Contact your local Altera representative for information on using a

PMC-Sierra interposer card with the development board.

To generate and monitor data traffic, you need an industry-standard

Gigabit Ethernet stimulus, capture, and analysis system. Optionally, you

can use an Agilent logic analysis system to probe the SPI-4.2 data in both

the receive and transmit directions.

Figure 8–1 illustrates the demonstration set-up using the Intel IXD1110

development board as an example.

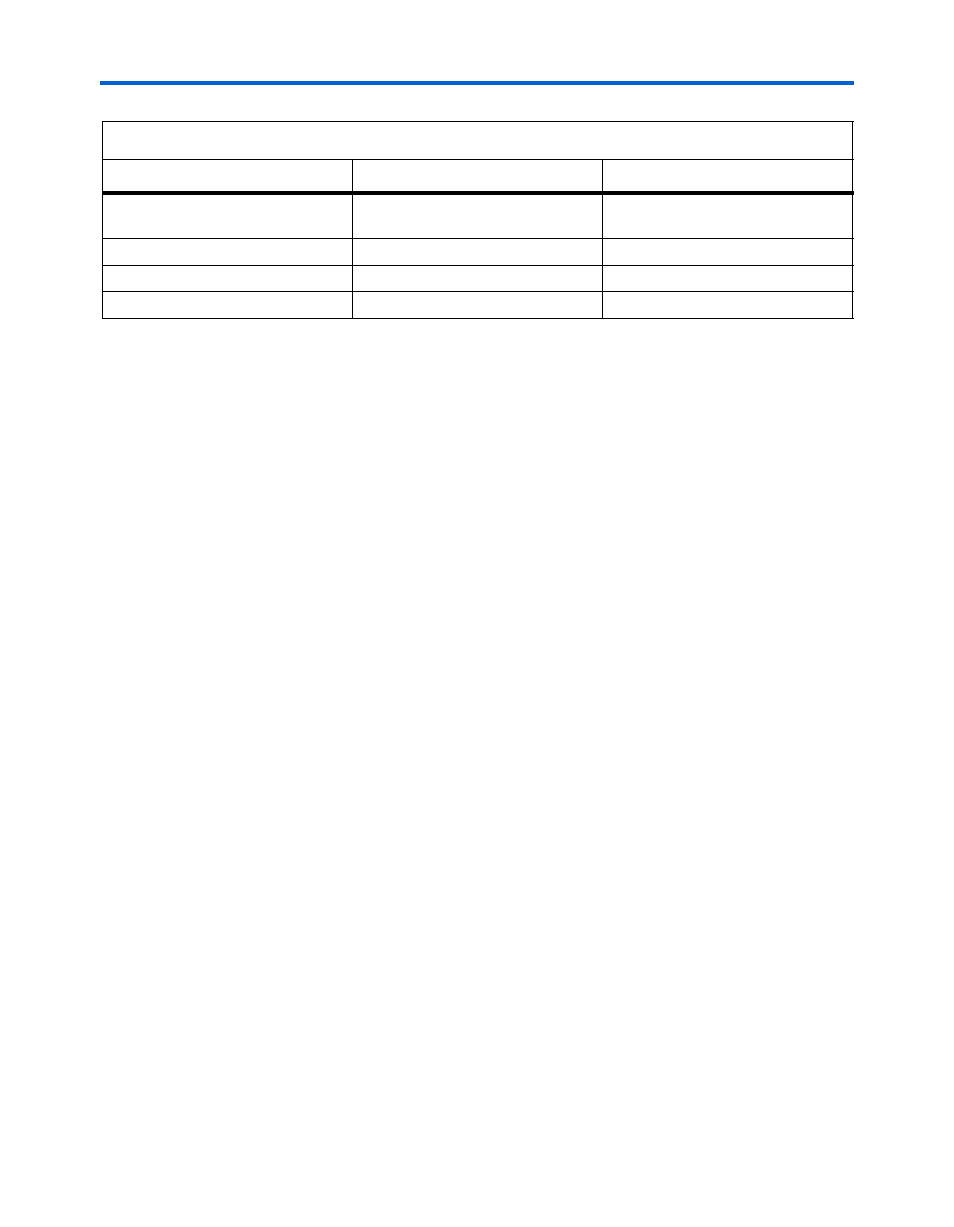

Maximum Training Sequence

Interval

-

32,000

Training Pattern Repetitions

-

32

Status Channel Clock Edge

Negative

Negative

Calendar Multiplier

1

1

Table 8–1. POS-PHY Level 4 MegaCore Configuration (Part 2 of 2)

Parameter

Receiver

Transmitter