Altera High-Speed Development Kit, Stratix GX Edition User Manual

Page 136

9–2

Quartus II Version 3.0

Altera Corporation

Introduction

High-Speed Development Kit, Stratix GX Edition User Guide

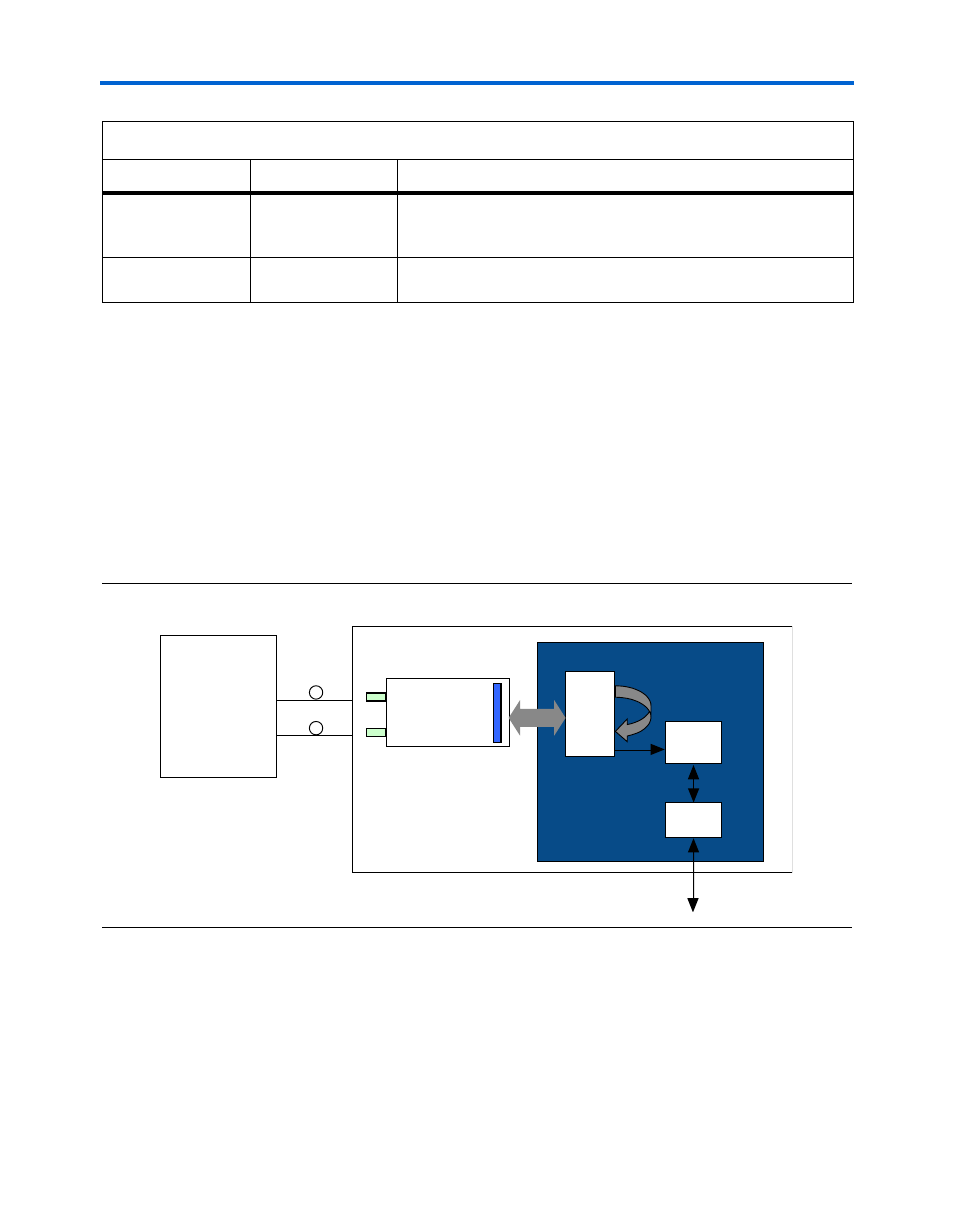

Figure 9–1 shows the application overview. A separate statistics module

implements 32-bit counters for received traffic statistics (e.g., packets

received, errors received). You can access these statistics through an

RS-232 connection that is served by an embedded Nios processor and a

small control application running on the processor. A normal RS-232

terminal program is sufficient to access the port. The RS-232 connection is

optional, that is, if it is not connected, the loopback operation is fully

functional as no specific configuration application needs to run on the

Nios processor.

The on-board Stratix GX LEDs indicate fault and traffic conditions.

Figure 9–1. Application Overview

1

The demonstration assumes that the optional XPAK

module is connected to the board and the 156.25 MHz clock

oscillator is enabled.

CRC append on

transmit

Enabled

Upon transmission, a new CRC is calculated and appended to each

frame. If the received frame had an error, the frame will be

transmitted with an error indication (XGMII error control code).

Padding remove

Enabled

If padded frames are received, the padding is removed. Upon

transmission the transmitter adds new padding.

Table 9–1. 10G Ethernet MAC Core Configuration (Part 2 of 2)

Parameter

Setting

Notes

Xpack

Module

10-Gigabit

Ethernet Tester

10GbE

MAC

Statistics

Module

Nios

RS-232

XAUI

Altera Board

Stratix GX Device