Altera High-Speed Development Kit, Stratix GX Edition User Manual

Page 129

Altera Corporation

Quartus II Version 3.0

8–1

8. Stratix GX SPI-4.2

Demonstration with 10-Port

Gigabit Ethernet MAC

The CD-ROM included with this kit has a device programming file that

demonstrates Stratix GX SPI-4.2 interoperability with the Intel

®

IXF1110

and PMC-Sierra S/UNI

®

-10xGE 10-port Gigabit Ethernet MAC devices.

The demonstration configures the Stratix GX device with Altera’s SPI-4.2-

compliant POS-PHY Level 4 MegaCore function with the receiver

connected to the transmitter over the Atlantic

™

interface for loopback

testing.

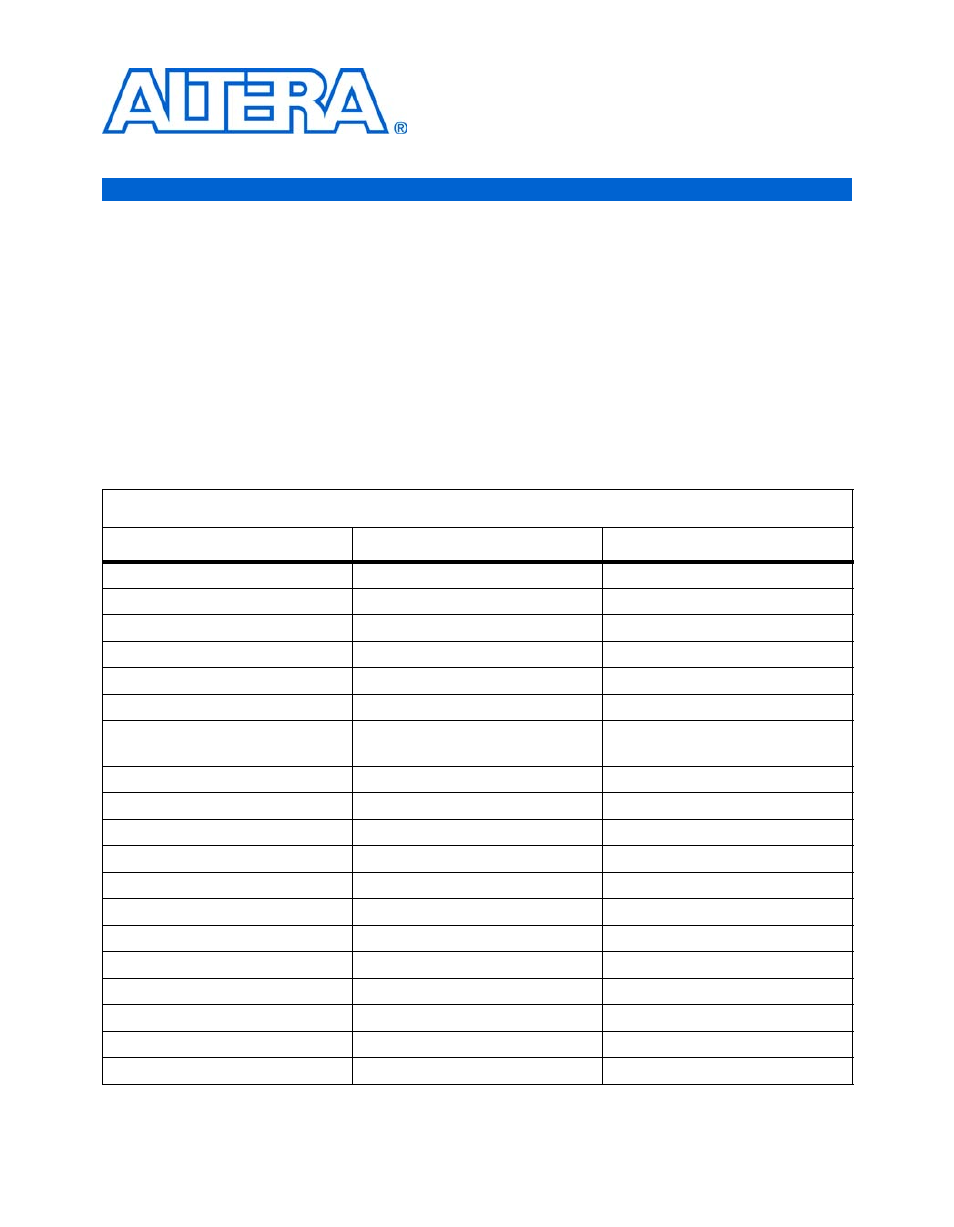

Table 8–1 describes the POS-PHY Level 4 parameters used in this

demonstration.

Table 8–1. POS-PHY Level 4 MegaCore Configuration (Part 1 of 2)

Parameter

Receiver

Transmitter

Device Family

Stratix GX

Stratix GX

Dynamic Phase Alignment

Yes

-

LVDS Data Rate

800 Mbps

800 Mbps

Data Path Width

128 bits

128 bits

Data Flow Direction

RX

TX

Number of Ports

10

10

Buffer Mode

Shared FIFO with Embedded

Addressing

Shared FIFO with Embedded

Addressing

FIFO Buffer Size

8,192 bytes

8,192 bytes

Almost Empty

512 bytes

-

Almost Full

1,024 bytes

MaxBurst1

-

512 bytes

MaxBurst2

-

1,024 bytes

Atlantic Data Width

128 bits

128 bits

FIFO Threshold Low

32 bytes

-

FIFO Threshold High

-

320 bytes

Transmit Bandwidth Optimization

-

No

Burst Mode

-

No

Burst Size

-

-

Multiple Continues

Yes

-