Stratix nios pmc test – Altera High-Speed Development Kit, Stratix GX Edition User Manual

Page 120

7–38

Quartus II Version 3.0

Altera Corporation

Nios Designs

High-Speed Development Kit, Stratix GX Edition User Guide

Stratix Nios PMC Test

This design comprises a Nios processor, a UART, and an Altera PCI core.

The design is captured in VHDL and has a VHDL wrapper to specify the

I/O pin names and placements. Because this a processor-based test, the

actual test consists of running several object files on the Nios processor

and observing the results in a terminal window on a PC.

The PMC interface test polls and initializes the attached PMC board. The

board is queried for its ID. If the board is a registered PMC board, the

shell displays the company name and board type.

f

Refer to “PMC Card Interface (Stratix Nios PMC)” on page 5–23 for

information on how to perform the test.

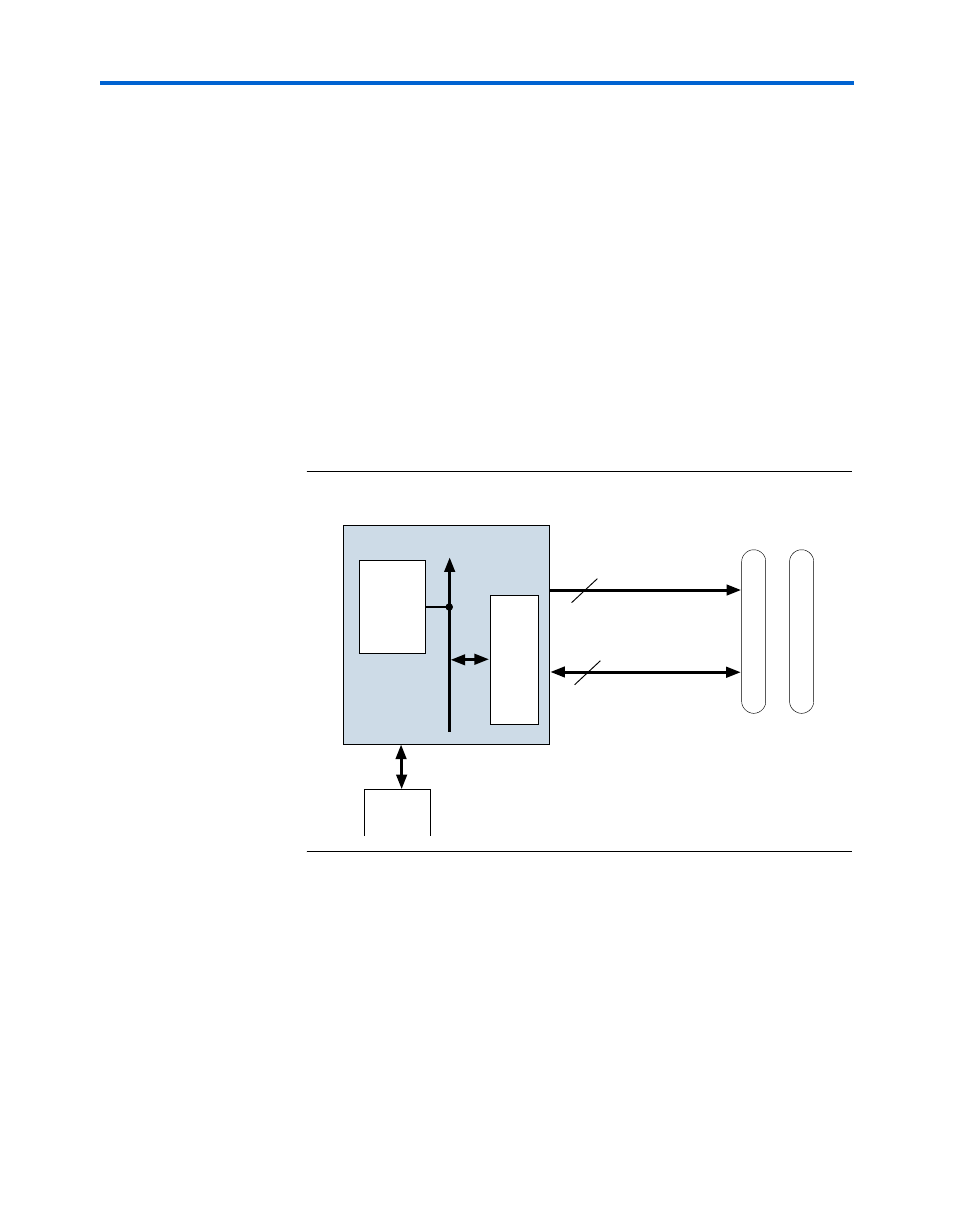

Figure 7–18 shows the Stratix Nios PMC logic diagram.

Figure 7–18. Stratix Nios PMC Logic Diagram

This design has a Nios CPU, a UART for external communication, and an

Altera PCI controller IP core. The PCI controller core acts as a bridge from

the internal Nios-based Avalon bus to a 33-MHz, 32-bit PCI bus. The core

can be configured as a master or target on the PCI bus. The core has a

32-bit PCI master/target interface, Nios target interface, DMA engine,

FIFO buffers, interrupt controller, and a host/arbiter.

f

For more information on Altera PCI cores, refer to Processors &

Preipherals in the IP section on the Altera web site.

PMC Status & Control

PMC AD[31:0]

18

32

PMC Interface

Connectors

RS-232

Port

Avalon

Bus

Stratix Device

Nios

CPU

Altera

PCI

IP

Core