2 rtm spi interface (slave), 3 mezzanine spi interface (slave), Table 8-2 – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 118: Rtm spi interface (slave), Table 8-3, Mezzanine spi interface (slave), Base artm fpga

Base ARTM FPGA

ARTM-831X Installation and Use (6806800M76E)

118

8.2.2

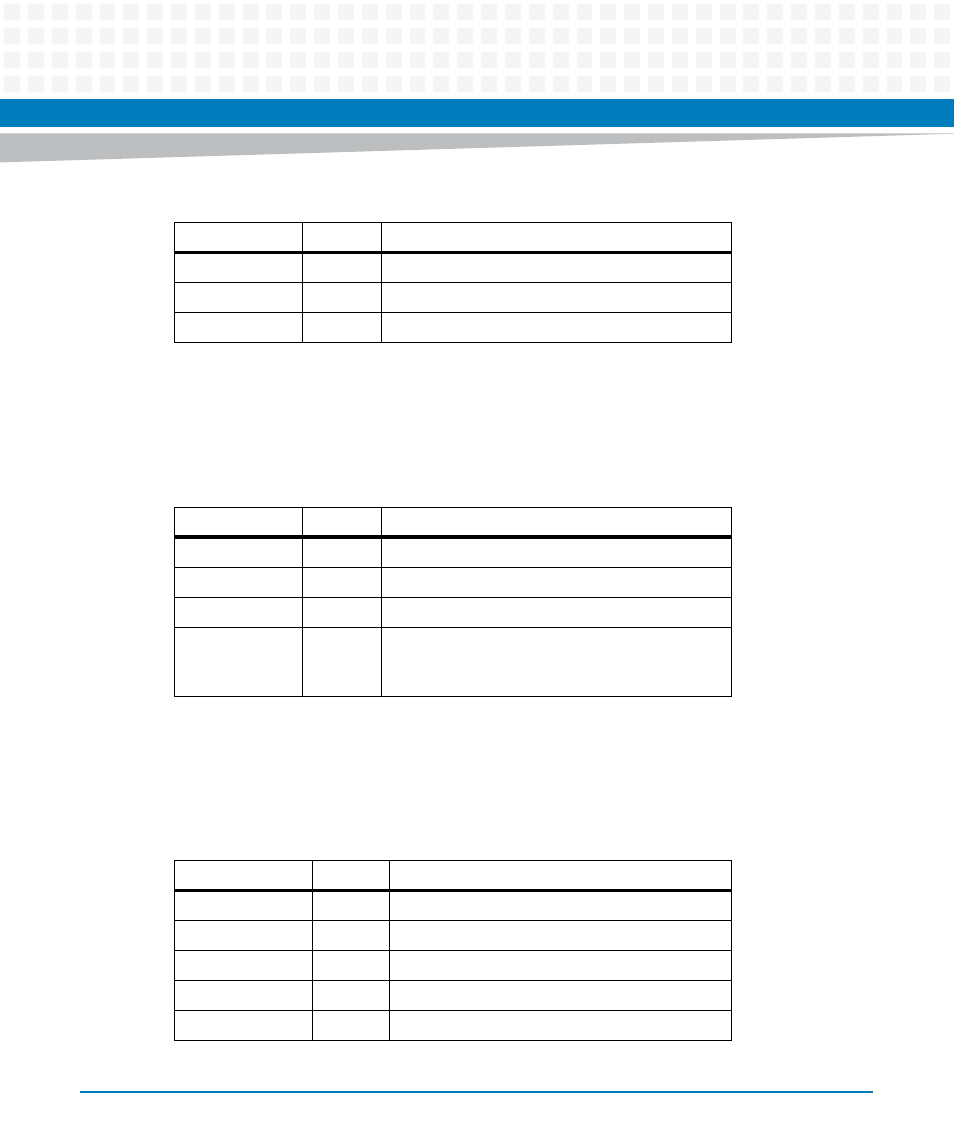

RTM SPI Interface (Slave)

The SPI Interface is used to access ARTM Base FPGA registers thru Glue Logic FPGA.

8.2.3

Mezzanine SPI Interface (Slave)

The SPI Interface is used to access ARTM Base FPGA registers from ARTM Mezzanine Card.

N54640_RST_

O

Buffered GE Reset form Zone 3

CLK_TSI

O

Master clock to TSI FPGA

CLK_EXT

O

Master clock to Extender FPGA

Table 8-1 Global Signals (continued)

Signal Name

Type

Description

Table 8-2 RTM SPI Interface (Slave)

Signal Name

Type

Description

RTM_SPI_SCK

I

ARTM SPI Clock

RTM_SPI_SS_

I

ARTM SPI select

RTM_SPI_MOSI

I

ARTM SPI Master Out Slave In

RTM_SPI_MISO

O

ARTM SPI Master In Slave Out. Used to Signal

interrupt to base board when RTM_SPI_SS_ is

inactive high.

Table 8-3 Mezzanine SPI Interface (Slave)

Signal Name

Type

Description

MEZZ_SPI_SCK

I

Mezzanine SPI Clock

MEZZ_SPI_SS_

I

Mezzanine SPI select

MEZZ_SPI_MOSI

I

Mezzanine SPI Master Out Slave In

MEZZ_SPI_MISO

O

Mezzanine SPI Master In Slave Out

MEZZ_SPI_INT_

O

Mezzanine SPI Interrupt