12 ge control register, Table 8-35, Telecom reference clock selection – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 137: Table 8-36, Ge control register, Base artm fpga

Base ARTM FPGA

ARTM-831X Installation and Use (6806800M76E)

137

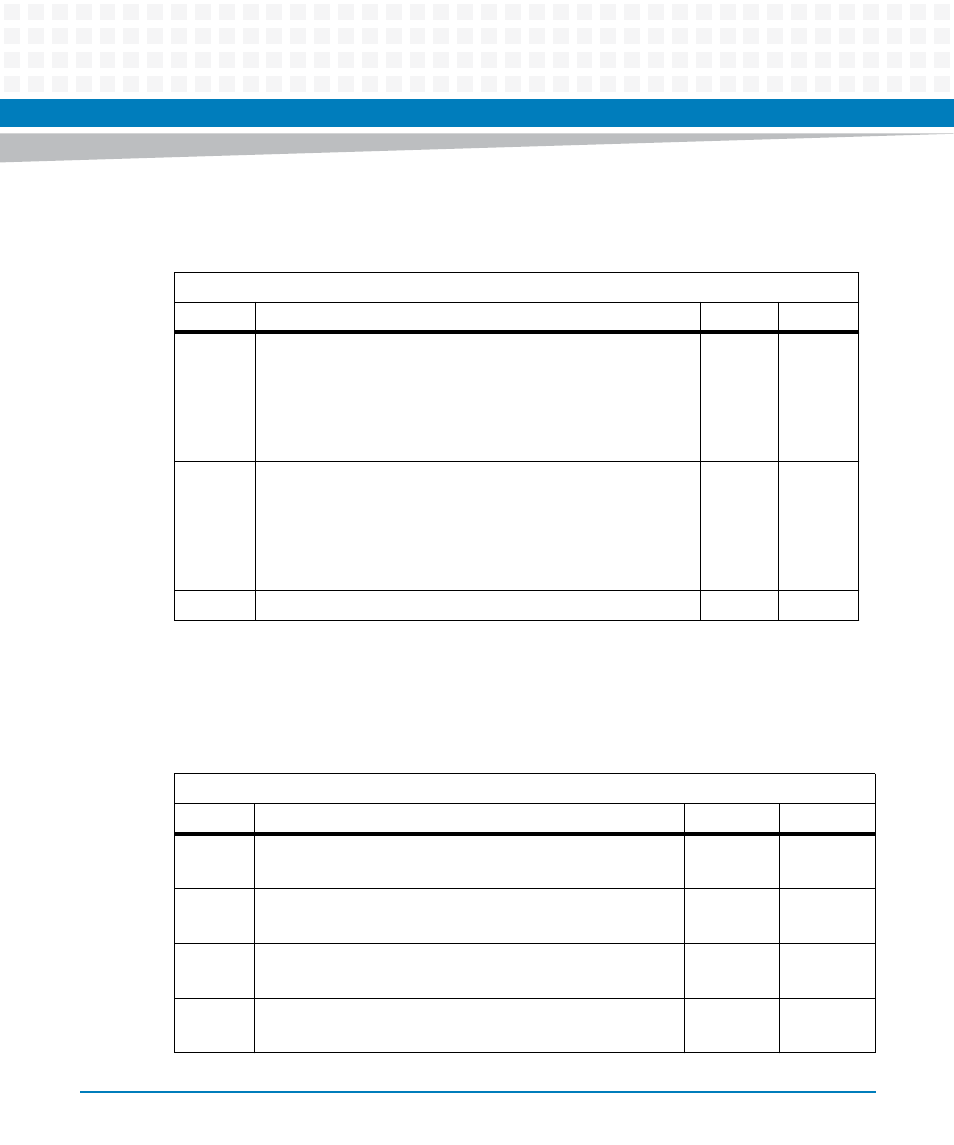

8.3.1.12 GE Control Register

Table 8-35 Telecom Reference Clock Selection

Address: 0x0B

Bit Description

Default

Access

1:0

Clock CLK_REFCLK_1 source selection:

b00: differential 10GE receive clock N8707_RCLK_P/M

b01: GE Receive clock 1 GE_RECCLK1

b10: GE Receive clock 1 GE_RECCLK2

b11: Reference clock control by Mezzanine Card

0

r/w

3:2

Clock CLK_REFCLK_2 source selection:

b00: differential 10GE receive clock N8707_RCLK_P/M

b01: GE Receive clock 1 GE_RECCLK1

b10: GE Receive clock 1 GE_RECCLK2

b11: Reference clock control by Mezzanine Card

0

r/w

7:4

Reserved

Table 8-36 GE Control Register

Address: 0x0C

Bit Description

Default

Access

0

Drive Signal N54640_ANEN

0

MMC: r

RTM: r/w

1

Drive Signal N54640_CRNT_LED_EN

0

MMC: r

RTM: r/w

2

Drive Signal N54640_F1000

0

MMC: r

RTM: r/w

3

Drive Signal N54640_FDX

0

MMC: r

RTM: r/w