Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 245

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

245

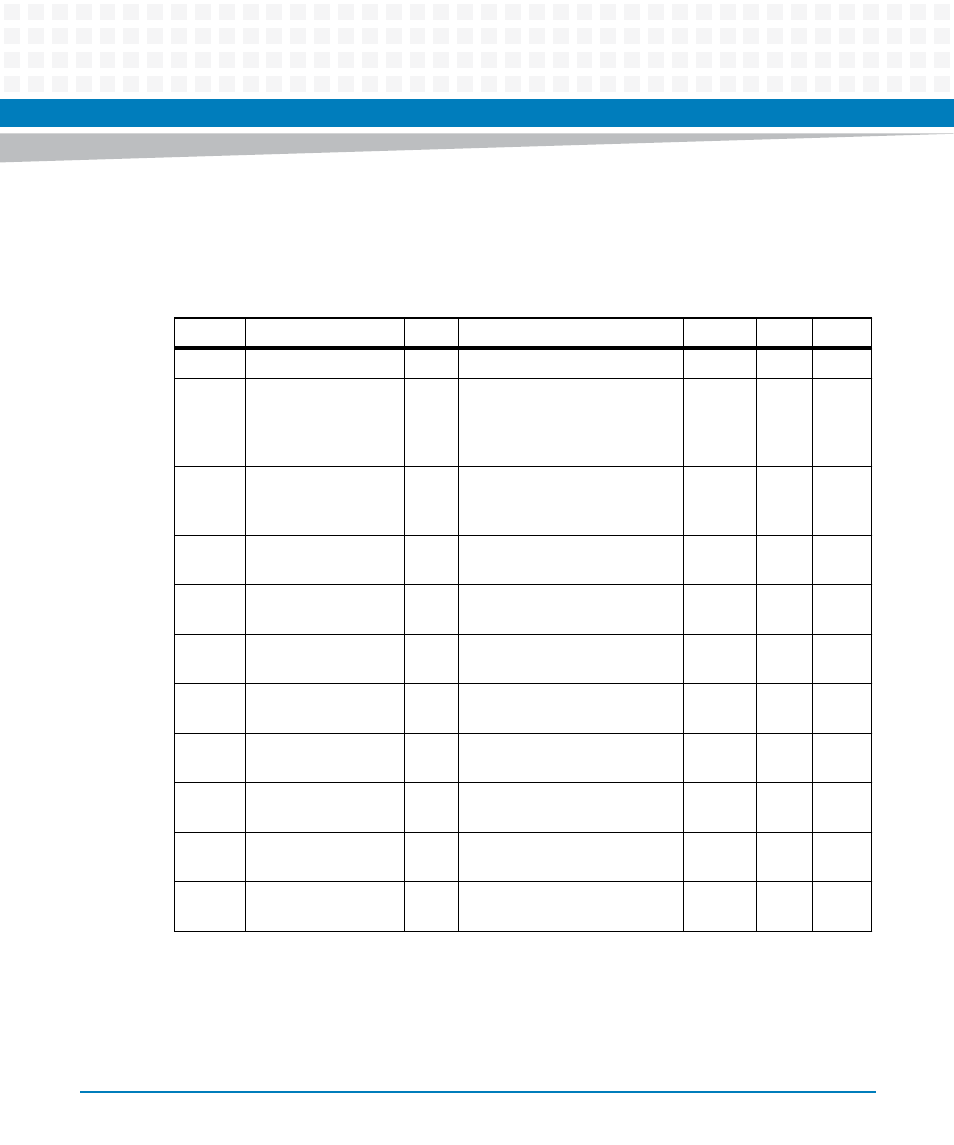

Width: 32 bit

The bits of this register reset the respective internal and external components, e.g. Xrt86

frame, etc. Writing a 1 to a bit puts the respective component into reset, until writing a 0 re-

enables its function again.

Bit

Acronym

Type

Description

Default

Pwr

Soft

31...14

-

-

reserved

undef

-

-

13

SrdsQdDmc12Reset

RW

0b1: SrdsQdDmc12Reset,

Serdes Quad of connections to

DMC 1 and 2 submodules is

reset

0b0

X

X

12

SrdsQdDmc0Reset

RW

0b1: SrdsQdDmc0Reset,

Serdes Quad of connection to

DMC 0 on baseboard is reset

0b0

X

X

11

Xrt75ChpReset3

RW

0b1: Xrt75ChpReset3, resets

the Xrt75 line interface unit 3

0b1

X

X

10

Xrt75ChpReset2

RW

0b1: Xrt75ChpReset2, resets

the Xrt75 line interface unit 2

0b1

X

X

9

Xrt75ChpReset1

RW

0b1: Xrt75ChpReset1, resets

the Xrt75 line interface unit 1

0b1

X

X

8

Xrt75ChpReset0

RW

0b1: Xrt75ChpReset0, resets

the Xrt75 line interface unit 0

0b1

X

X

7

Xrt86ChpReset5

RW

0b1: Xrt86ChpReset5, resets

the Xrt86 framer 5

0b1

X

X

6

Xrt86ChpReset4

RW

0b1: Xrt86ChpReset4, resets

the Xrt86 framer 4

0b1

X

X

5

Xrt86ChpReset3

RW

0b1: Xrt86ChpReset3, resets

the Xrt86 framer 3

0b1

X

X

4

Xrt86ChpReset2

RW

0b1: Xrt86ChpReset2, resets

the Xrt86 framer 2

0b1

X

X