Tsi fpga, 23spi 1 bus access monitor register, 24spi 1bus access monitor reset register – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 255

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

255

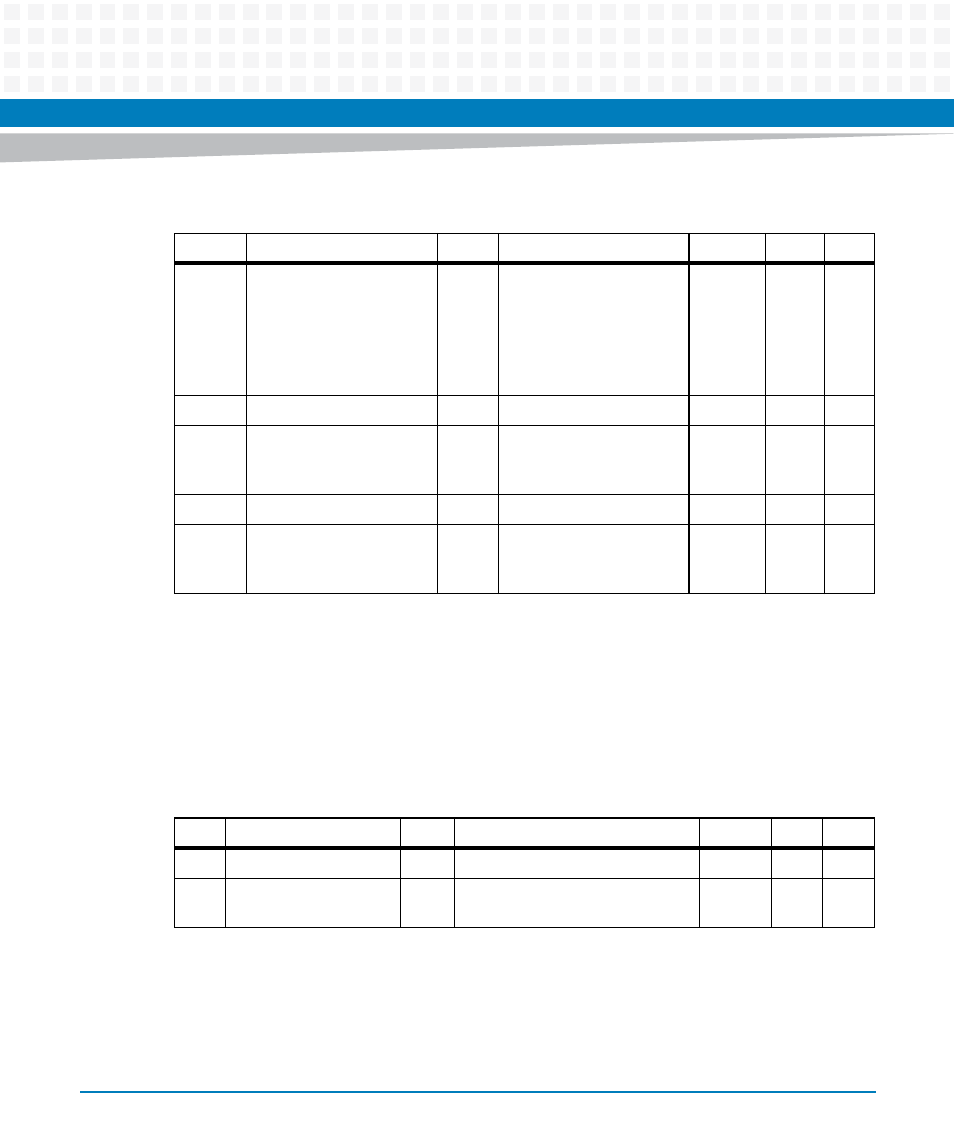

This register stores the address of the last timed out access at the local bus.

9.5.2.11.23Spi 1 Bus Access Monitor Register

Address:

0x14A0, Spi1BusMonReg

Width: 8 bit

This register monitors the access to the local bus.

9.5.2.11.24Spi 1Bus Access Monitor Reset Register

Address:

0x14A1, Spi1BusMonResetReg

Bit

Acronym

Type

Description

Default

Pwr

Soft

31

LclBusAccessedDirection

R

0b1: LclBusAccessWrite,

A address has been

written with timeout

0b0: LclBusAccessRead, A

address has been read

with timeout

0b0

F

F

30...24

-

-

reserved

undef

-

-

23...20

LclBusAccessedSelects

R

The selects recorded

during the last timedout

access to the local bus

0x0

F

F

19

-

-

reserved

undef

-

-

18...0

LclBusAccessedAddress

R

The address recorded

during the last timedout

access at the local bus

0x0

F

F

Bit

Acronym

Type

Description

Default

Pwr

Soft

7...1

-

-

reserved

undef

-

-

0

Spi1BusAccessTimeout R

0b1: Spi1BusAccessTimeout, An

access to the Spi1 bus timed out

0b0

F

F