Tsi fpga, 9 debug led register, 10synchronisation select register – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 241

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

241

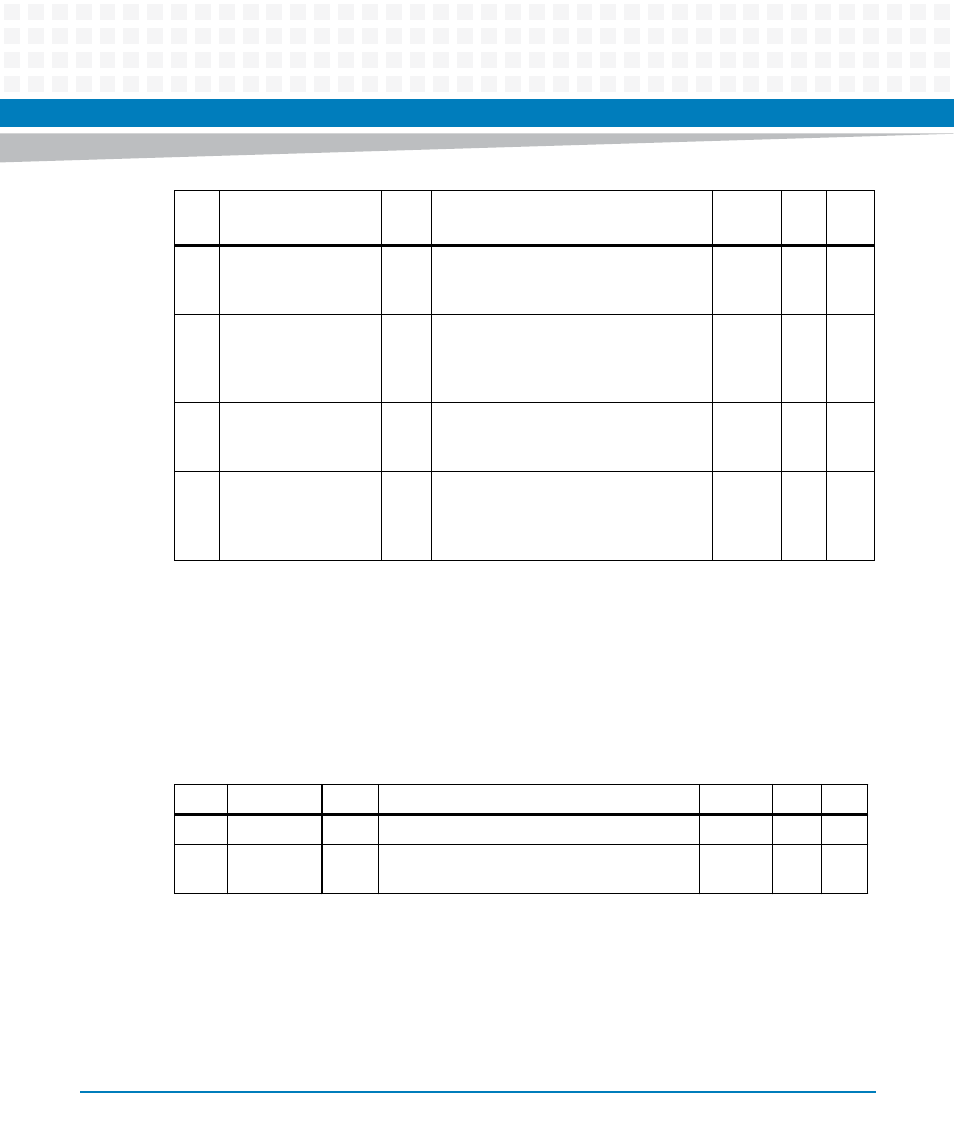

9.5.2.11.9 Debug LED Register

Address:

0x1424, DebugLedReg

Width: 8 bit

This register controls the condition of the lower 3 LEDs for Debug purposes.

9.5.2.11.10Synchronisation Select Register

Addresses:

0x1430, SyncSelReg00

0x1434, SyncSelReg01

3

NoTdmEsfSyncIntrpt

Mask

RW

0b1: NoTdmEsfSyncEnable, enables no

main extended superframe 166.66Hz

sync pulse indicator

0b0

X

X

2

NoMainTdmSyncPuls

eIntrptMask

RW

0b1: NoMainTdmFrameSyncEnable,

enables no main frame sync 8kHz pulse

from TDM system clock generator

indicator

0b0

X

X

1

NoMainClkPllLock77I

ntrptMask

RW

0b1: NoMainClkPllLock77Enable,

enables main clock PLL 77.76 MHz not

locked to TDM system clock indicator

0b0

X

X

0

NoMainClkPllLock13

1IntrptMask

RW

0b1: NoMainClkPllLock131Enable,

enables main clock PLL 131.072MHz

not locked to TDM system clock

indicator

0b0

X

X

Bit

Acronym

Type

Description

Default

Pwr

Soft

Bit

Acronym

Type

Description

Default

Pwr

Soft

7...3

-

-

reserved

undef

-

-

2...0

DebugLed

RW

Debug LED port, a LED is on if the respective

bit is 1

0b000

X

X