22 telecom reference clock divider registers, Table 8-46, Telecom reference clock divider refclk1 register – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 144: Table 8-47, Telecom reference clock divider refclk2 register, Base artm fpga

Base ARTM FPGA

ARTM-831X Installation and Use (6806800M76E)

144

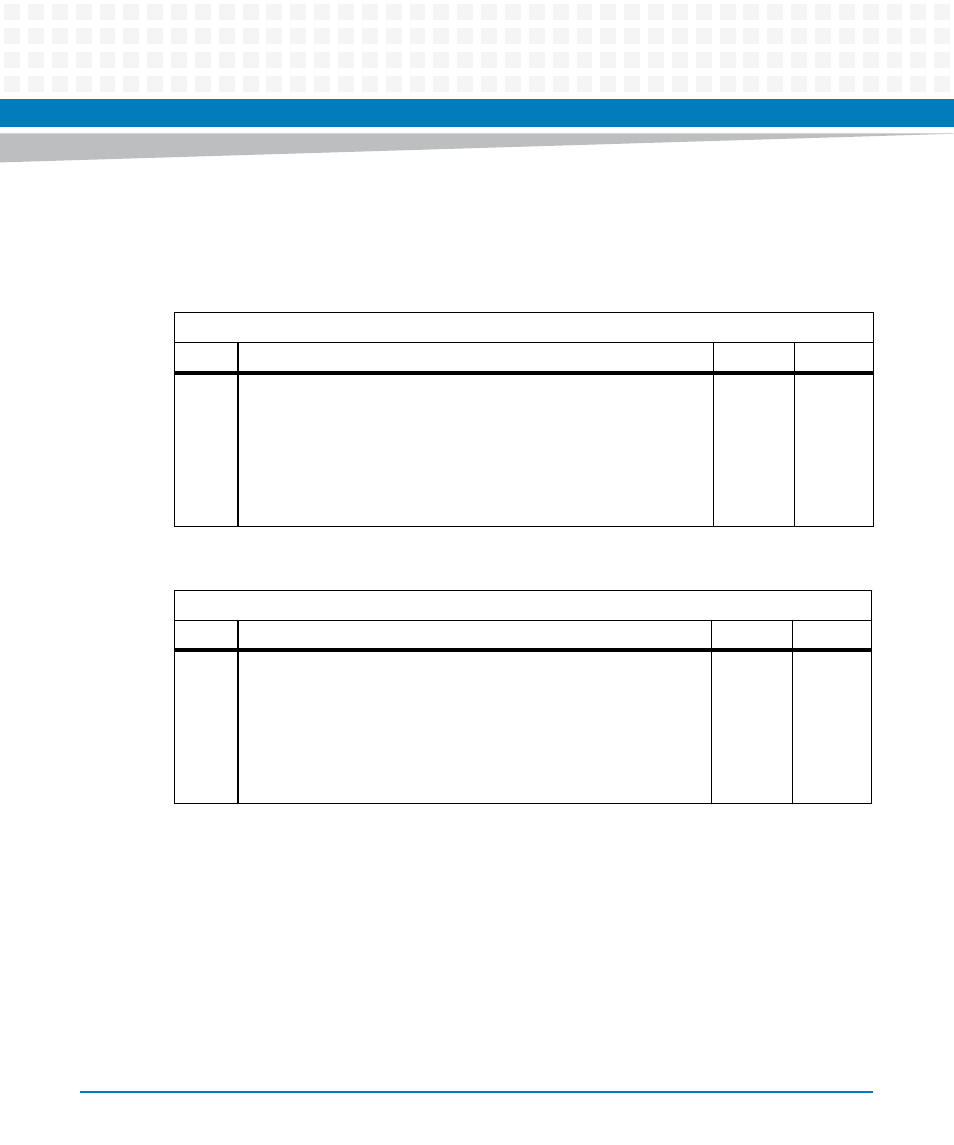

8.3.1.22 Telecom Reference Clock Divider Registers

Table 8-46 Telecom Reference Clock Divider REFCLK1 Register

Address: 0x18 - 0x19

Bit Description

Default

Access

15:0

CLK_REFCLK_1 divider value:

0: No Clock. Drive CLK_REFCLK_1 low

1: Bypass selected clock

1 < N < 65536: Divide source clock by N.

For even N values the duty cycle is 50%

For odd N values the duty cycle is 50% plus 50*(1/N).

0

r/w

Table 8-47 Telecom Reference Clock Divider REFCLK2 Register

Address: 0x1A - 0x1B

Bit Description

Default

Access

15:0

CLK_REFCLK_2 divider value:

0: No Clock. Drive CLK_REFCLK_ low

1: Bypass selected clock

1 < N < 65536: Divide source clock by N.

For even N values the duty cycle is 50%

For odd N values the duty cycle is 50% plus 50*(1/N).

0

r/w