Table 9-16, Pci base address register 2, Table 9-17 – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 286: Pci subsystem vendor register, Table 9-18, Pci subsystem id register, Tsi fpga

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

286

31:11

Base Address used to map Secondary I/O (2048B) into PCI IO

space

PCI_RST_: 0

PCI: r/w

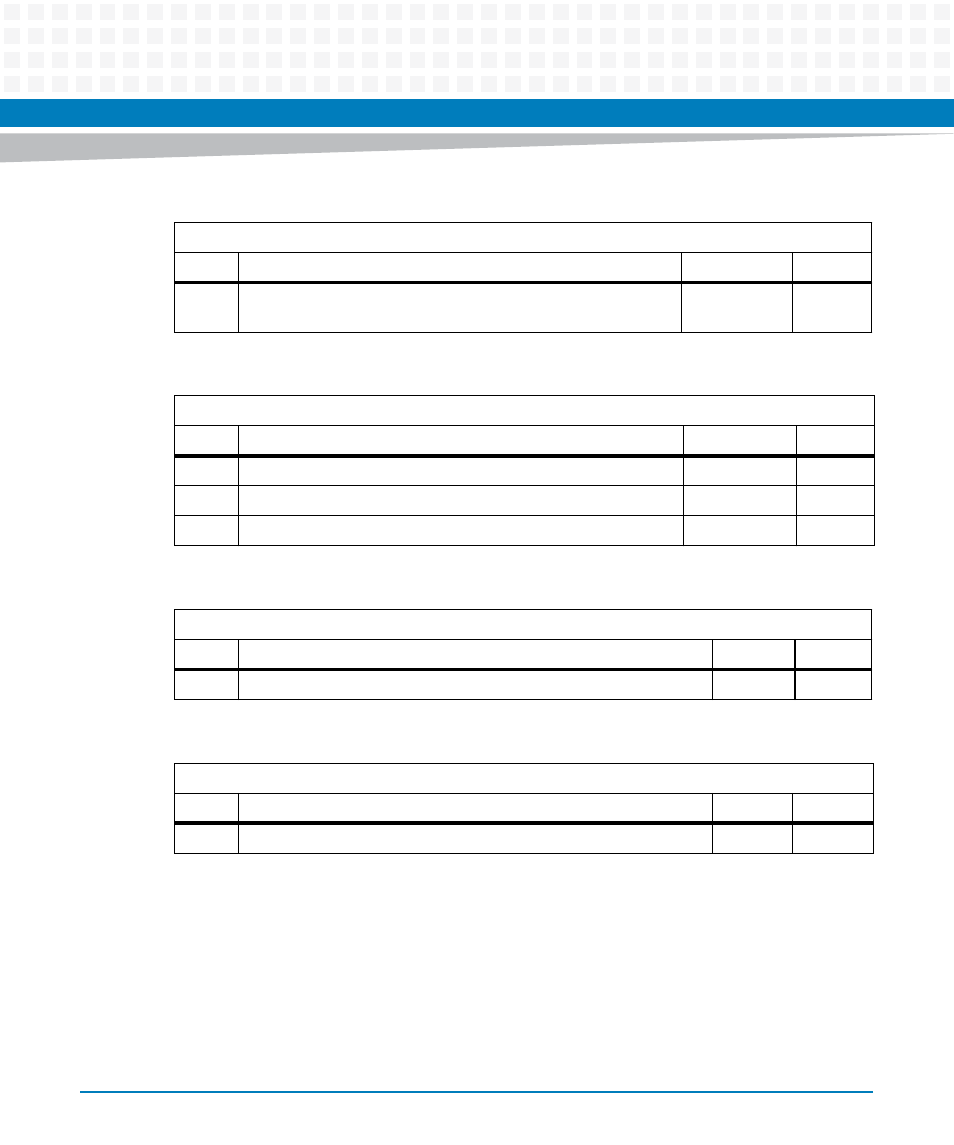

Table 9-16 PCI Base Address Register 2

PCI Configuration Offset: 0x18

Bit Description

Default

Access

0

IO Space indicator

1

PCI: r

6:1

Hardcoded

0

PCI: r

31:7

Base Address used to map Primary I/O (128B) into PCI IO space.

PCI_RST_: 0

PCI: r/w

Table 9-17 PCI Subsystem Vendor Register

PCI Configuration Offset: 0x2C

Bit Description

Default

Access

15:0

Subsystem vendor ID (unique add-in board vendor ID)

0x1223

PCI: r

Table 9-18 PCI Subsystem ID Register

PCI Configuration Offset: 0x2E

Bit Description

Default

Access

15:0

Subsystem ID. Unique add-in board device ID

0x8310

PCI: r

Table 9-15 PCI Base Address Register 1 (continued)

PCI Configuration Offset: 0x14

Bit Description

Default

Access