Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 227

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

227

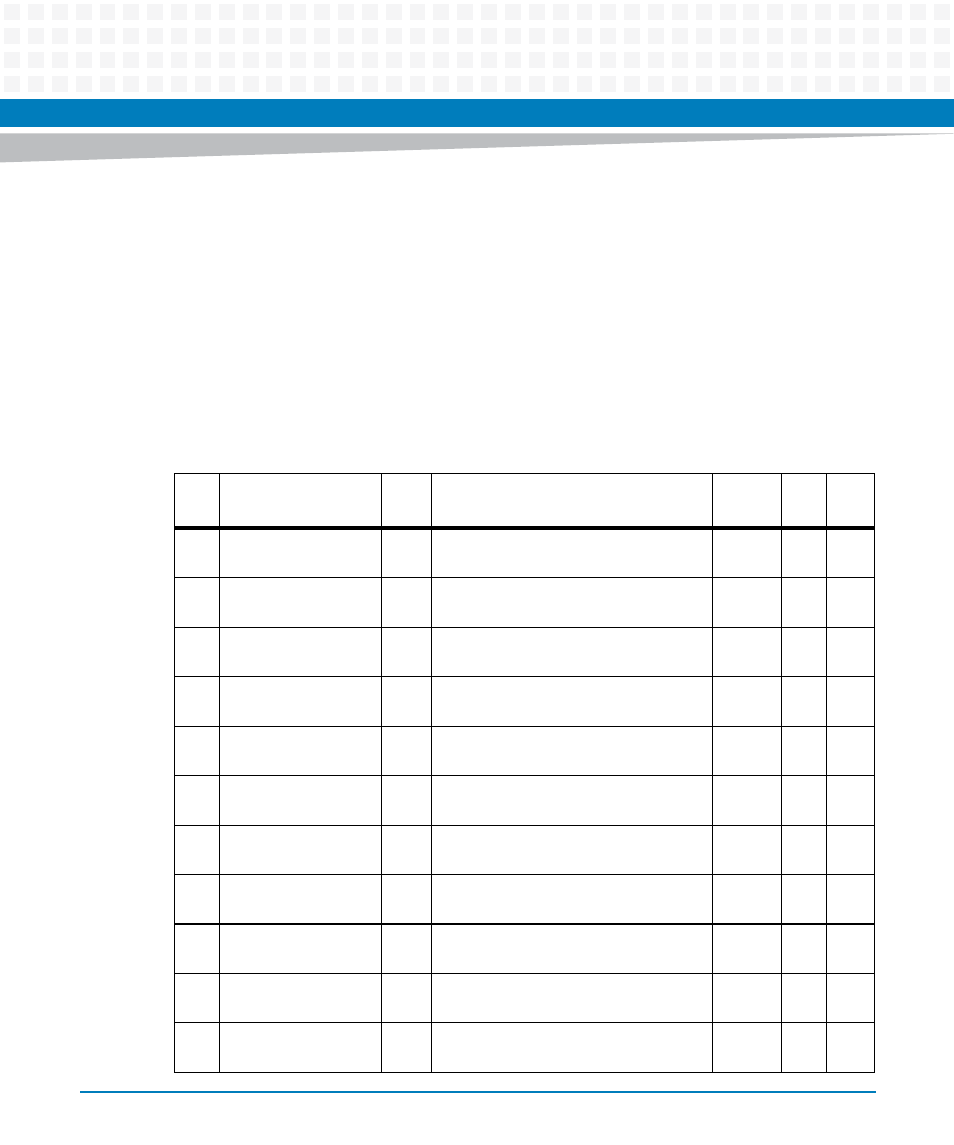

0x1324, TohCtrReg11

0x1328, TohCtrReg12

0x132C, TohCtrReg13

Width: 32 bit

The RtmFpga connects to 2 Sonet/Sdh-framers. Each framer may connect to 4 STM1/OC3 data

streams, each containing E1,2 and D1..12 DCCbytes in similar fashion.

This results in a total of 8 registers to enable the insertion of data from respective TSI channels

by the framer at its add interface.

Bit

Acronym

Type

Description

Default

Pwr

Soft

31..

.18

-

-

reserved

undef

-

-

17

EnE2

RW

0b1: EnE2, enables the insertion of

channel data from TSI into E2

0b0

X

X

16

EnE1

RW

0b1: EnE1, enables the insertion of

channel data from TSI into E1

0b0

X

X

15..

.12

-

-

reserved

undef

-

-

11

EnD12

RW

0b1: EnD12, enables the insertion of

channel data from TSI into D12

0b0

X

X

10

EnD11

RW

0b1: EnD11, enables the insertion of

channel data from TSI into D11

0b0

X

X

9

EnD10

RW

0b1: EnD10, enables the insertion of

channel data from TSI into D10

0b0

X

X

8

EnD9

RW

0b1: EnD9, enables the insertion of

channel data from TSI into D9

0b0

X

X

7

EnD8

RW

0b1: EnD8, enables the insertion of

channel data from TSI into D8

0b0

X

X

6

EnD7

RW

0b1: EnD7, enables the insertion of

channel data from TSI into D7

0b0

X

X

5

EnD6

RW

0b1: EnD6, enables the insertion of

channel data from TSI into D6

0b0

X

X