10 transport overhead registers (tohregs), Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 226

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

226

0x1254, DispErrCntReg1

0x1294, DispErrCntReg2

Width: 32 bit

This register indicates the number of the Disparity errors since enabling the Disparity error

counting by the ErrCntCtrlReg:DispErrCntStart bit. The error counter sticks at 0xFFFFFF.

Reg0 is for Serdes-connection to the BaseBoard, Reg1 to DMC1 and Reg2 to DMC2.

9.5.2.10 Transport Overhead Registers (TohRegs)

Resets:

Pwr = Power on reset

Soft = Soft reset

Transport Overhead Registers for E1,2 and D1..12 DCC bytes insertion/extraction

9.5.2.10.1 Transport Overhead Control Register

Addresses:

0x1300, TohCtrReg00

0x1304, TohCtrReg01

0x1308, TohCtrReg02

0x130C, TohCtrReg03

0x1320, TohCtrReg10

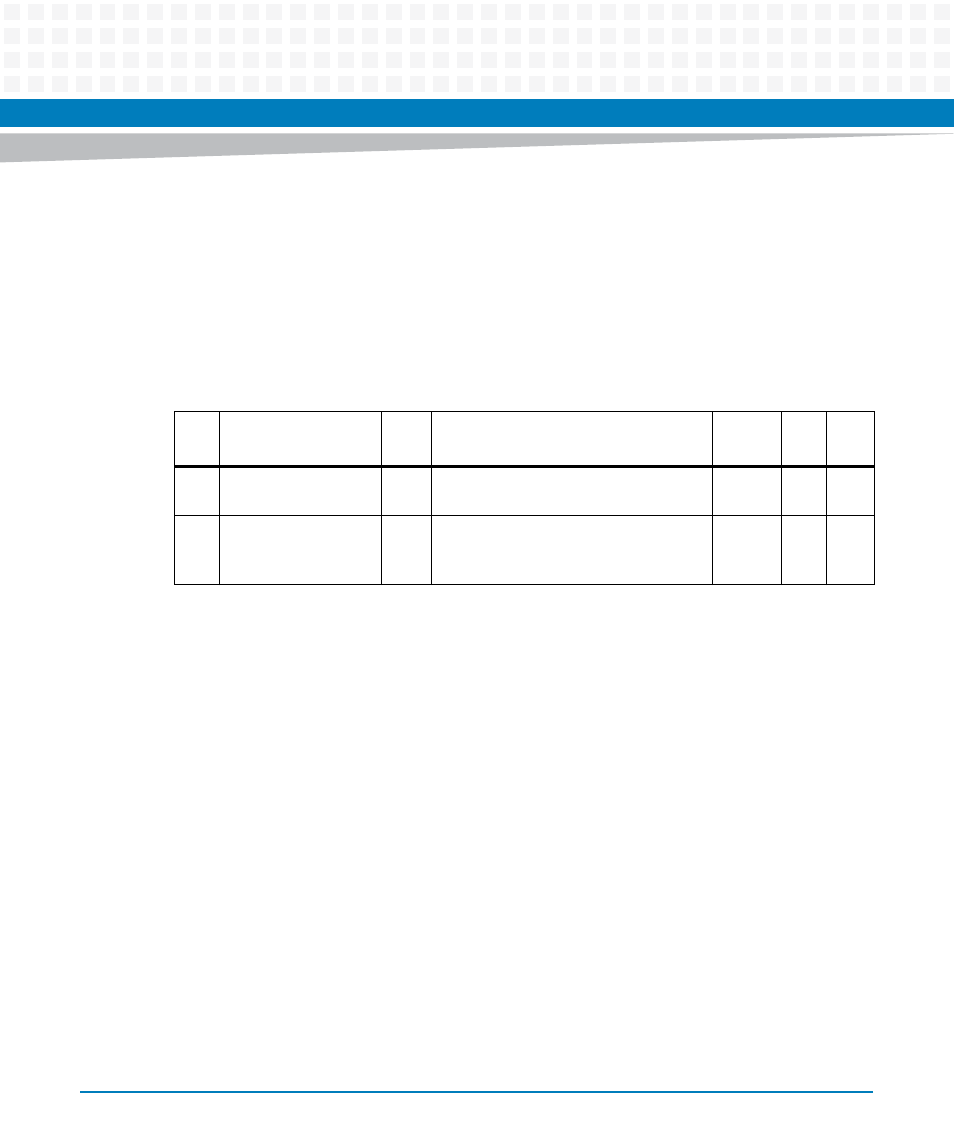

Bit

Acronym

Type

Description

Default

Pwr

Soft

31..

.24

-

-

reserved

undef

-

-

23..

.0

DispErrCnt

R

This register indicates the number of

Disparity errors. The error counter

sticks at 0xFFFFFF

0x0

F

F