Tsi fpga, 6 test frame count register – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 223

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

223

This register controls the error counter of static test pattern received via the supplementary

channel, it controls the error counter for CRC error rate evaluation and the counter totally

transferred frame counter.

Reg0 is for Serdes-connection to the BaseBoard, Reg1 to DMC1 and Reg2 to DMC2.

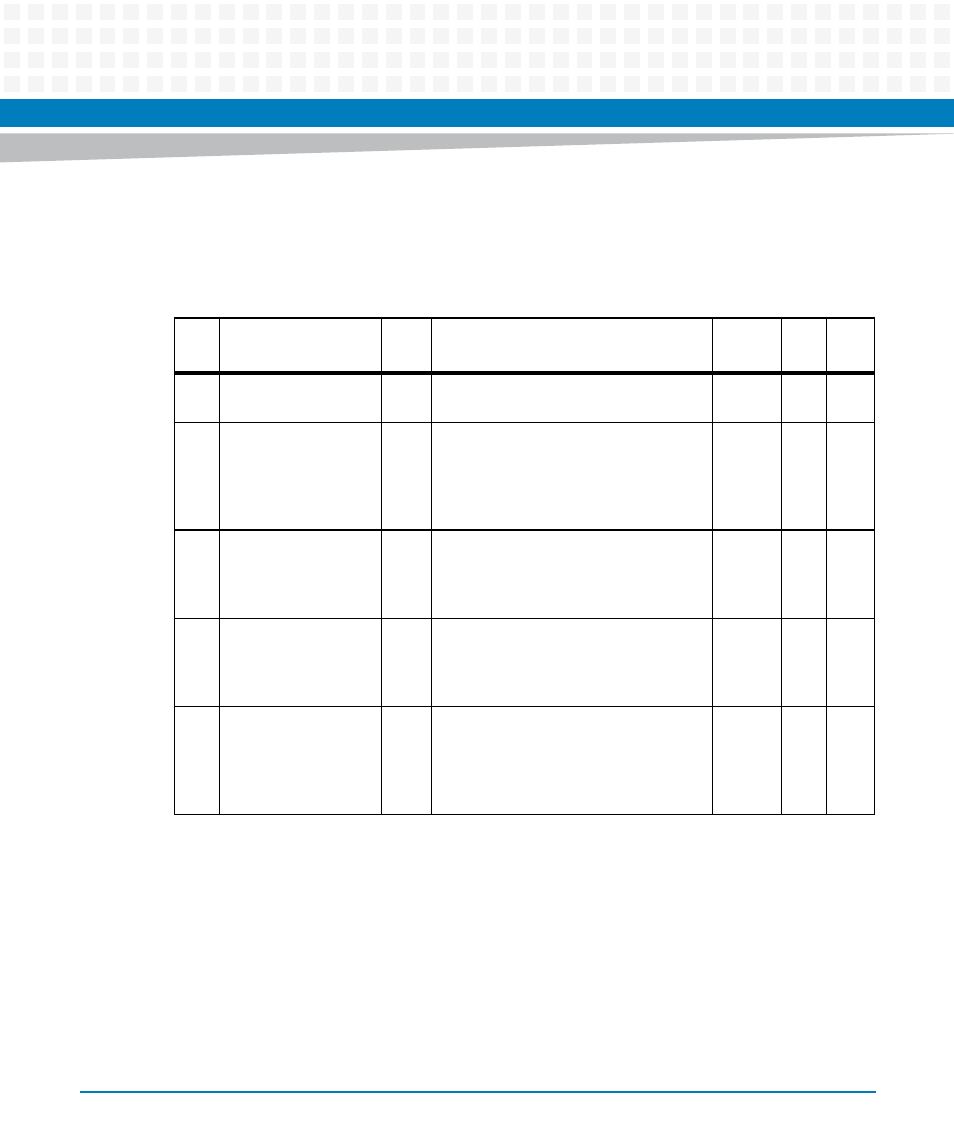

9.5.2.9.6 Test Frame Count Register

Addresses:

0x1208, TstFrameCntReg0

0x1248, TstFrameCntReg1

0x1288, TstFrameCntReg2

Width: 32 bit

Bit

Acronym

Type

Description

Default

Pwr

Soft

7...

4

-

-

reserved

undef

-

-

3

FrameCntRun

RW

0x1: FrameCntRun, starts frame

counting for test pattern and CRC error

rate evaluation. TstFrameCntReg is

cleared by changing the value of this bit

from 0 to 1.

0b0

X

X

2

DispErrCntRun

RW

0x1: DispErrCntRun, starts Disparity

error counting. DispErrCntReg is

cleared by changing the value of this bit

from 0 to 1.

0b0

X

X

1

CrcErrCntRun

RW

0x1: CrcErrCntRun, starts CRC error

counting. CrcErrCntReg is cleared by

changing the value of this bit from 0 to

1.

0b0

X

X

0

SupplTstPatErrCntRu

n

RW

0x1: SupplTstPatErrCntRun, starts

pattern error counting.

SupplTstPatErrCntReg is cleared by

changing the value of this bit from 0 to

1..

0b0

X

X