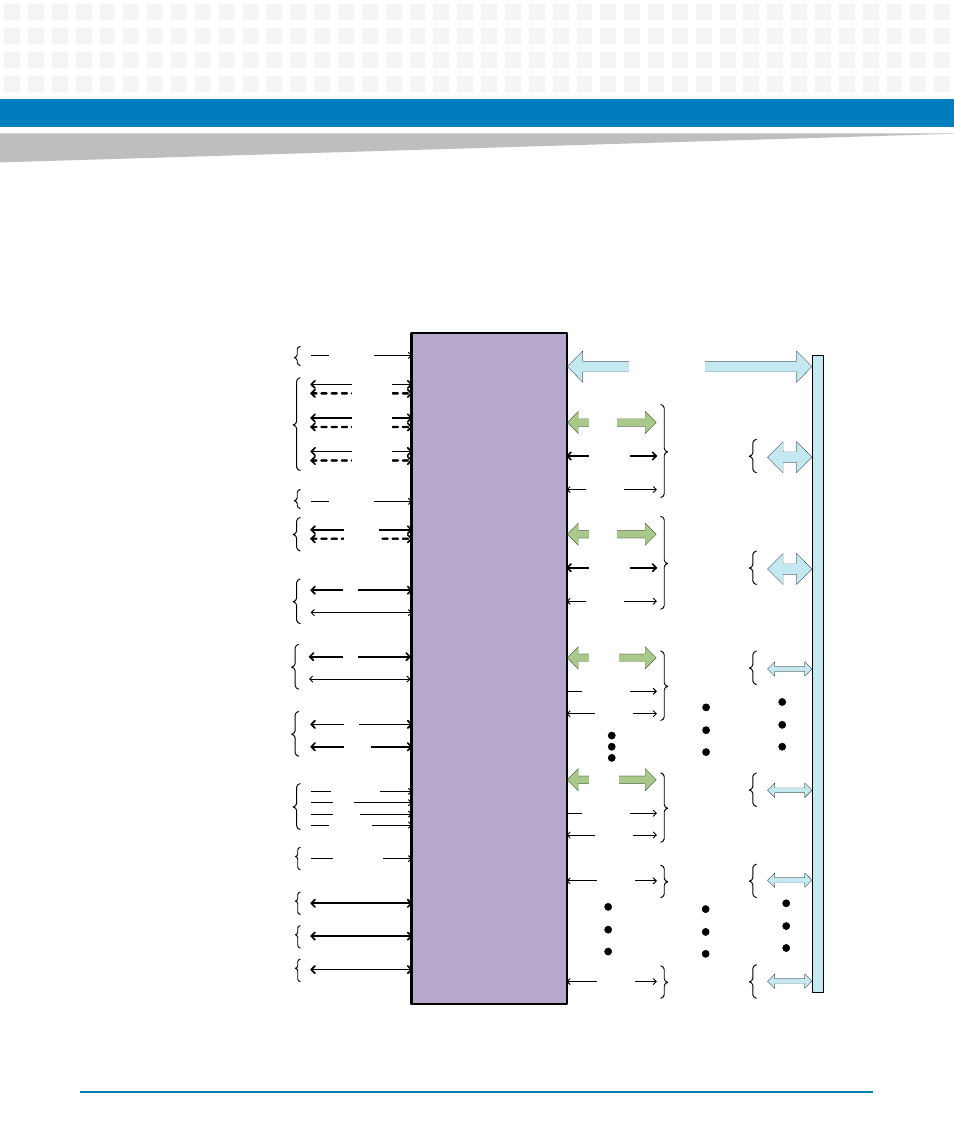

3 tsi fpga signals overview, Figure 9-2, Overview of tsi fpga signals – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 162: Rtm fpga, Tsi fpga, Figure 9-2 overview of tsi fpga signals

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

162

9.3

TSI FPGA Signals Overview

Figure 9-2

Overview of TSI FPGA Signals

SerDes links to Dsp-

pools on baseboard

and 2 submodules

2.5Gb or

2x1.25Gb

2.5Gb or

2x1.25Gb

2.5Gb or

2x1.25Gb

PCIE1.0

x1 or x2

PCIE links to host

bridgeD

2x Interrupt ,

2x Reset

2x DS26503 Bits

framer

SPI

Interrupt,

Reset

ExtFpga pin

extention

SPI

Serial Configuration

Flash

SPI

Config

Glue Fpga

6x tbd.

Led, Debug

Leds, DebugPins

32.768MHz

8kHz

166Hz

Reference Clock

2x125MHz

Reference Clock

1x100MHz

Basic TDM clock,

Framesync and

Multiframesync

Basic Reset

PowerGood

Test

Jtag

16Bit Addressbus,

16Bit Databus,

Rd, Wr, 8xCs,Rdy

PMC8310

Framer 0

SBITR

Bus 0

Overhead

Interface

77.76MHz

HMVIP

Bus 0

32.768MHz

Xrt86

Framer 0

HMVIP

Bus 5

32.768MHz

Xrt86

Framer 5

Interrupt,

Reset

Interrupt,

Reset

SBITR

Bus 1

Overhead

Interface

PMC8310

Framer 1

Interrupt,

Reset

Interrupt,

Reset

Xrt75

Liu0

Interrupt ,

Reset

Xrt75

Liu0

Interrupt ,

Reset

16Bit Data

16Bit Data

8Bit Data

8Bit Data

8Bit Data

8Bit Data

RTM

FPGA