Tsi fpga, 14component event status register – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 246

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

246

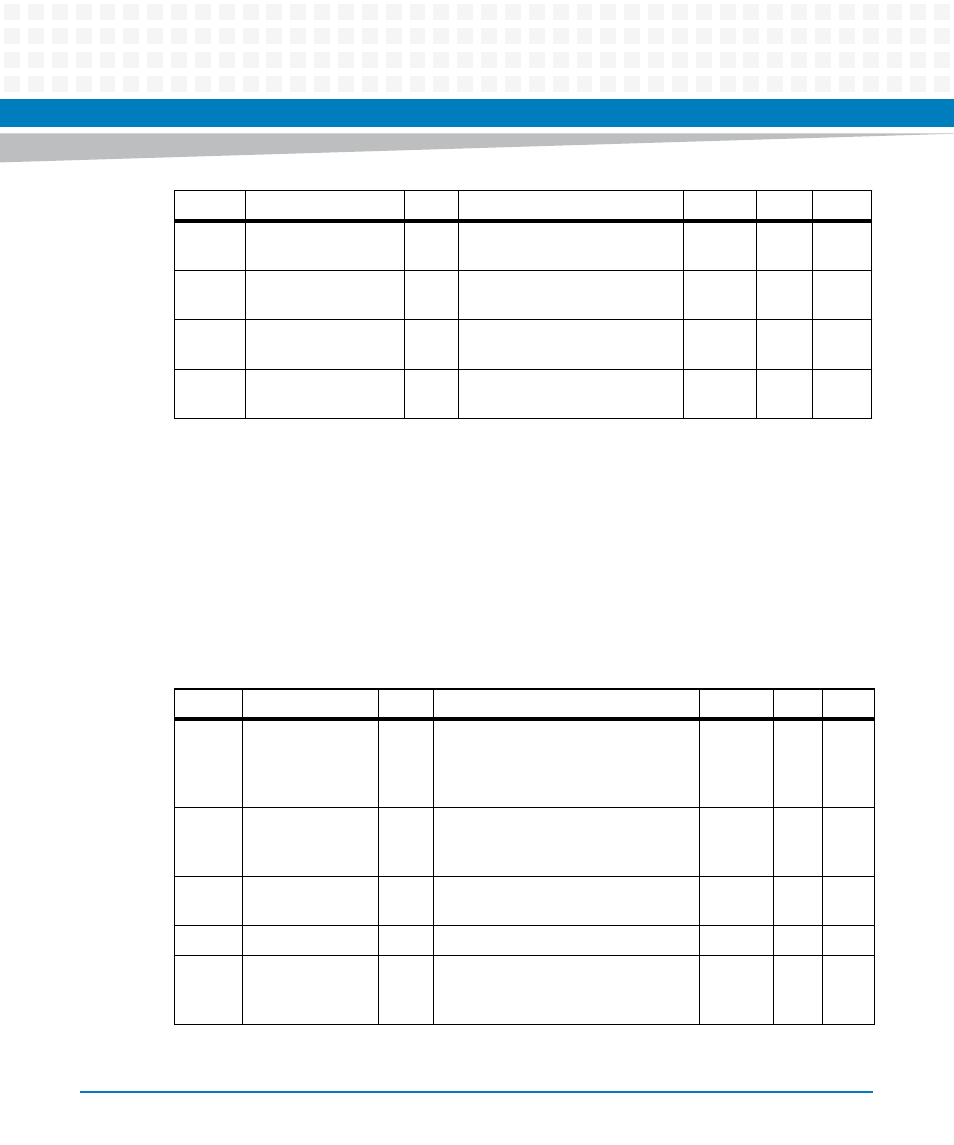

9.5.2.11.14Component Event Status Register

Address:

0x1474, CompEvtReg

Width: 32 bit

This register monitors the internal and external components, eg. Xrt86 framer, interrupt

status. If an interrupt occurs, the respective bit is set. It can be reset by writing the respective

bit in ExtCompEvtReg.

3

Xrt86ChpReset1

RW

0b1: Xrt86ChpReset1, resets

the Xrt86 framer 1

0b1

X

X

2

Xrt86ChpReset0

RW

0b1: Xrt86ChpReset0, resets

the Xrt86 framer 0

0b1

X

X

1

Pmc83ChpReset1

RW

0b1: Pmc83ChpReset1, resets

the Pmc8310 framer 1

0b1

X

X

0

Pmc83ChpReset0

RW

0b1: Pmc83ChpReset0, resets

the Pmc8310 framer 0

0b1

X

X

Bit

Acronym

Type

Description

Default

Pwr

Soft

Bit

Acronym

Type

Description

Default

Pwr

Soft

31

Gr8Intrpt

R

0b1: Gr8Intrpt, active when the Gr8

block switches its pages of receive

and transmit message data link

memory (9ms interval)

undef

-

-

30

Spi2Intrpt

R

0b1: Spi2Intrpt, active if the Spi bus 2

(from BaseExtFpga) signals an

interrupt

undef

-

-

29

Spi1Intrpt

R

0b1: Spi1Intrpt, active if the Spi bus 1

(from ExtFpga) signals an interrupt

undef

-

-

28...12

-

-

reserved

undef

-

-

11

Xrt75ChpIntrpt3

R

0b1: Xrt75ChpIntrpt3, active if the

Xrt75 line interface unit 3 has

signalled an interrupt

0b0

F

F