Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 243

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

243

These registers determine the superframe synchronization of the exar framers: Ds1 Esf, Ds1 SF

or E1 mode. Each HMVIP interface of the framers is partitioned into two parts, which can be

synchronized separately. The first digit of the indize numbers a framer chip and the second a

partition of this framer.

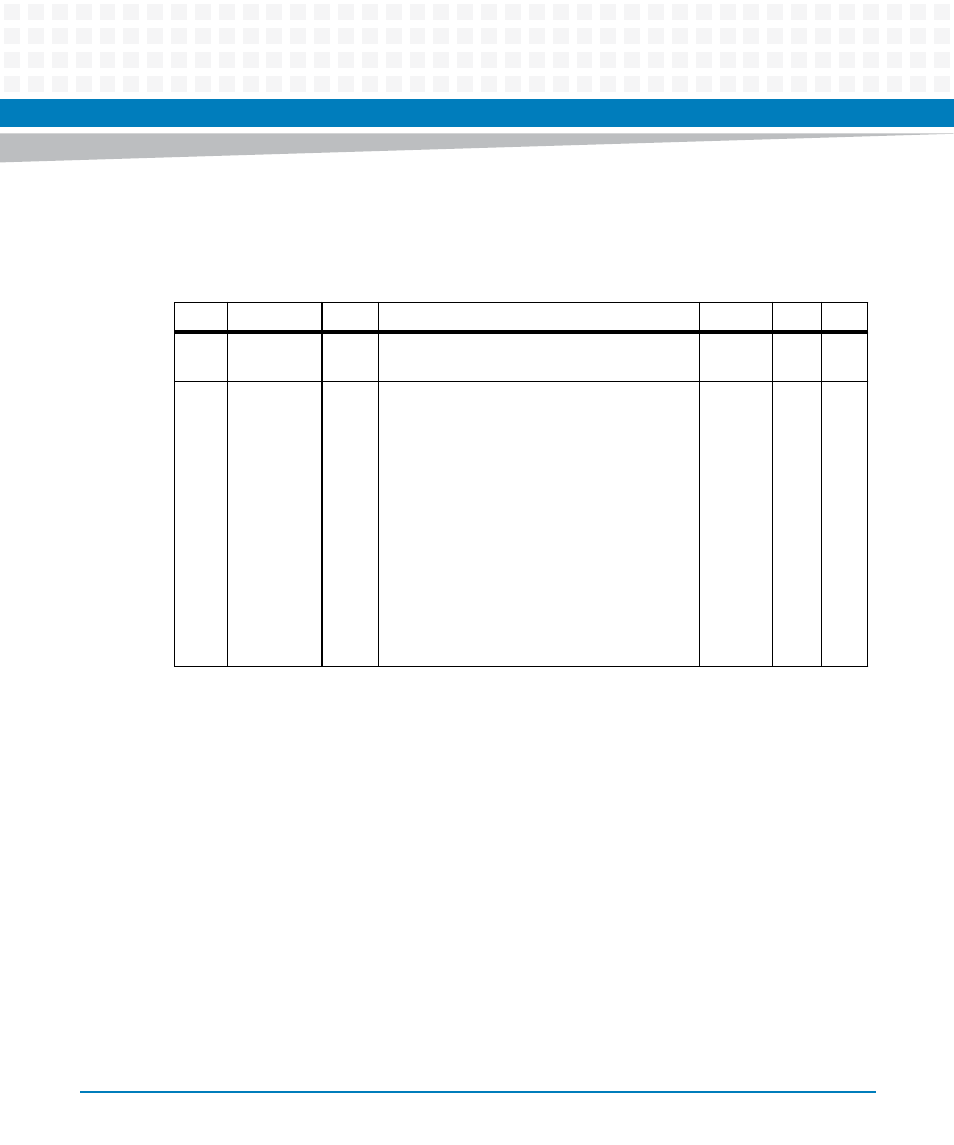

9.5.2.11.11Path Overhead Partner Mfs Offset Register

Address:

0x1460, PohPartnerMfsOffsetReg

Width: 8 bit

Bit

Acronym

Type

Description

Default

Pwr

Soft

31...

2

-

-

reserved

undef

-

-

1...0

ExarFrame

SyncSel

RW

Select of Exar Frame Sync Timing:

0b00: FrSyDs1Esf_3000usSel, Select of frame

sync timing for Ds1 extended superframe

sync 3ms interval

0b01: FrSyDs1Sf_1500usSel, Select of frame

sync timing for Ds1 extended superframe

sync 1.5ms interval

0b10: FrSyE1Sf_2000usSel, Select of frame

sync timing for Ds1 extended superframe

sync 2ms interval

0b11: FrSyPlain_125usSel, Select of plain

125us frame sync timing for Ds1 extended

superframe

0b0

X

X