Ext fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 332

EXT FPGA

ARTM-831X Installation and Use (6806800M76E)

332

0xC0, SelRclk2

0xC4, SelRclk3

Width: 32 bit

The registers control which of 8 recovered line clocks from XRT86 framer chips 2...5 or which

of 6 recovered line clocks from upto 4 line interfaces XRT75 is switched to the respective

ExtFpgaRLClk2 or ExtFpgaRLClk3 output of the ExtFpga (SelRclk2 determines

RtmExtFpgaRLClk2, SelRclk3 determines RtmExtFpgaRLClk3. The RtmExtFpgaRLClk2 and 3

are connected to the BaseExtFpga on the front board which finally decides which RCLK to put

for synchronization to the central TDM clock generator. Depending on the module type, not all

clock sources may be present.

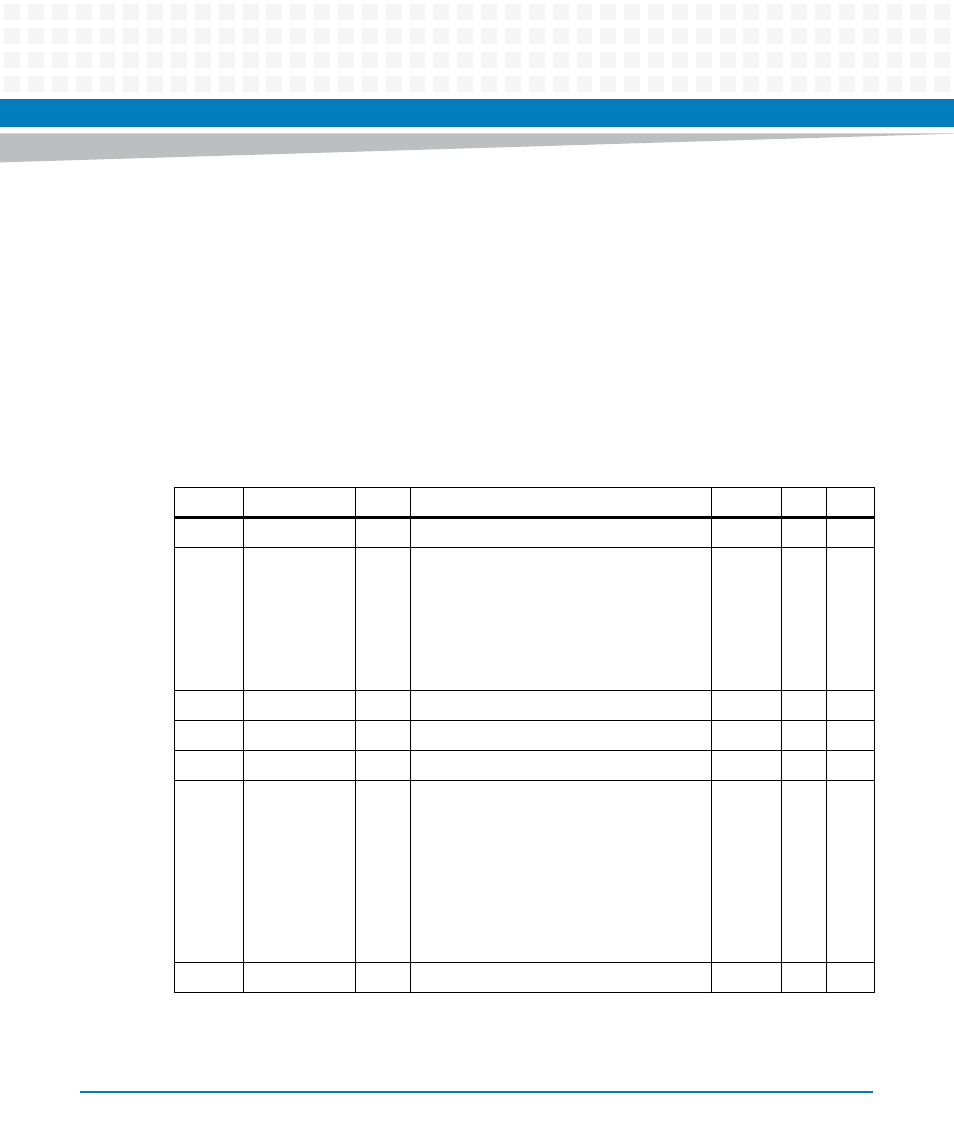

Bit

Acronym

Type

Description

Default

Pwr

Soft

31...26

-

-

reserved

undef

-

-

25...24

SrcBlkRLclkSe

l

RW

0b00: reserved

0b01: Xrt86BlkSel, Select clock from

Xrt86 block

0b10: Xrt75BlkSel, Select clock from

Xrt75 block

0b11: reserved

0b00

X

X

23...22

-

-

reserved

undef

-

-

21...20

-

-

reserved

undef

-

-

15...14

-

-

reserved

undef

-

-

13...12

Xrt75OutChi

pSel

RW

0b00: Xrt75OutChip0Sel, Select framer

chip 0

0b01: Xrt75OutChip1Sel, Select framer

chip 1

0b10: Xrt75OutChip2Sel, Select framer

chip 2

0b11: Xrt75OutChip3Sel, Select framer

chip 3

0b00

X

X

11

-

-

reserved

undef

-

-