Tsi fpga, 5 status xrt86 framer transmitter register – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 277

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

277

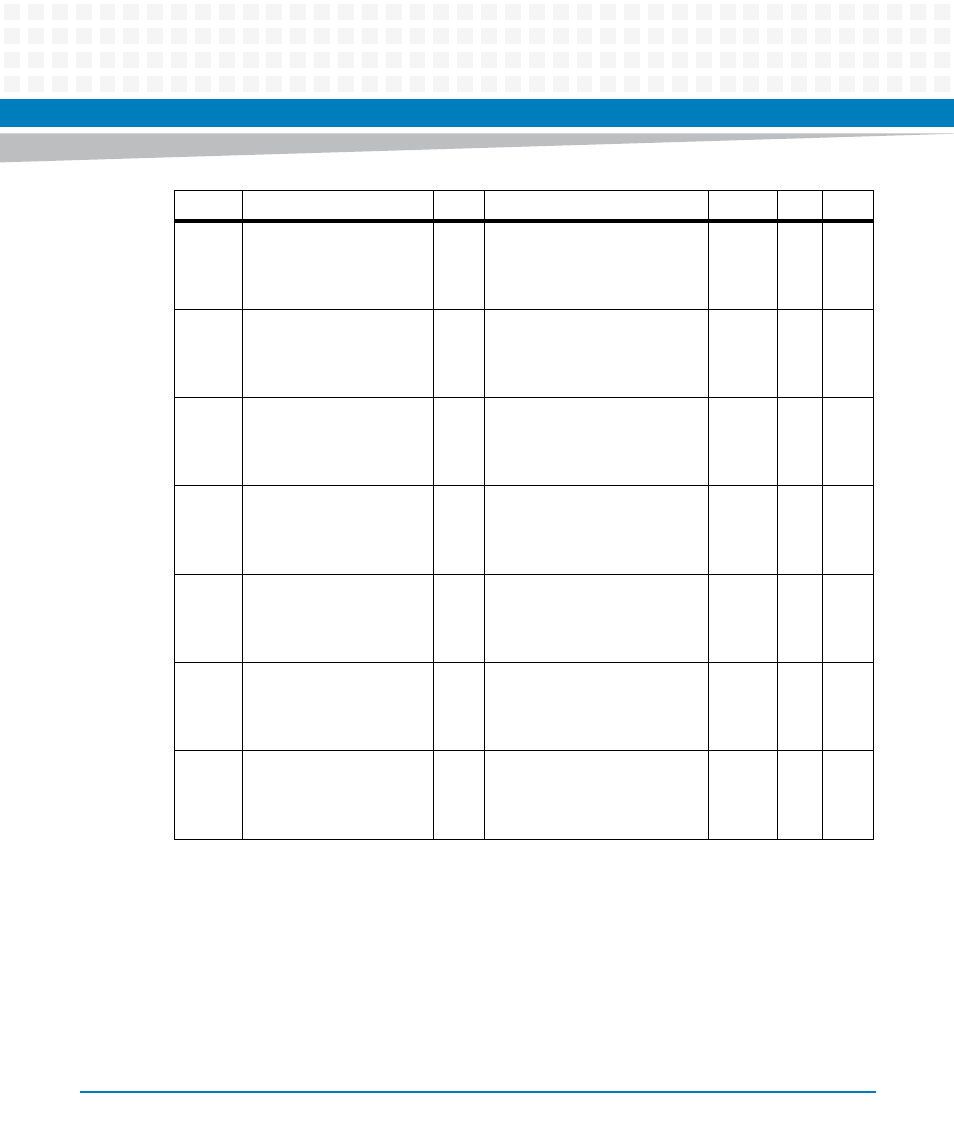

9.5.2.13.5 Status Xrt86 Framer Transmitter Register

Address:

0x1620, StatXrt86FrmTrmReg

Width: 8 bit

6

Xrt86Chp0RcvLoSIntrpt

Mask6

RW

0b1:

Xrt86Chp0RcvLoSIntrptEnabl

e6, enables chip 0 receiver Line

6 loss of signal interrupt bit

0b0

X

X

5

Xrt86Chp0RcvLoSIntrpt

Mask5

RW

0b1:

Xrt86Chp0RcvLoSIntrptEnabl

e5, enables chip 0 receiver Line

5 loss of signal interrupt bit

0b0

X

X

4

Xrt86Chp0RcvLoSIntrpt

Mask4

RW

0b1:

Xrt86Chp0RcvLoSIntrptEnabl

e4, enables chip 0 receiver Line

4 loss of signal interrupt bit

0b0

X

X

3

Xrt86Chp0RcvLoSIntrpt

Mask3

RW

0b1:

Xrt86Chp0RcvLoSIntrptEnabl

e3, enables chip 0 receiver Line

3 loss of signal interrupt bit

0b0

X

X

2

Xrt86Chp0RcvLoSIntrpt

Mask2

RW

0b1:

Xrt86Chp0RcvLoSIntrptEnabl

e2, enables chip 0 receiver Line

2 loss of signal interrupt bit

0b0

X

X

1

Xrt86Chp0RcvLoSIntrpt

Mask1

RW

0b1:

Xrt86Chp0RcvLoSIntrptEnabl

e1, enables chip 0 receiver Line

1 loss of signal interrupt bit

0b0

X

X

0

Xrt86Chp0RcvLoSIntrpt

Mask0

RW

0b1:

Xrt86Chp0RcvLoSIntrptEnabl

e0, enables chip 0 receiver Line

0 loss of signal interrupt bit

0b0

X

X

Bit

Acronym

Type

Description

Default

Pwr

Soft