19 configuration signals, Table 8-19, Dedicated configuration signals – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 127: Table 8-20, Dual-purpose configuration signals, Base artm fpga

Base ARTM FPGA

ARTM-831X Installation and Use (6806800M76E)

127

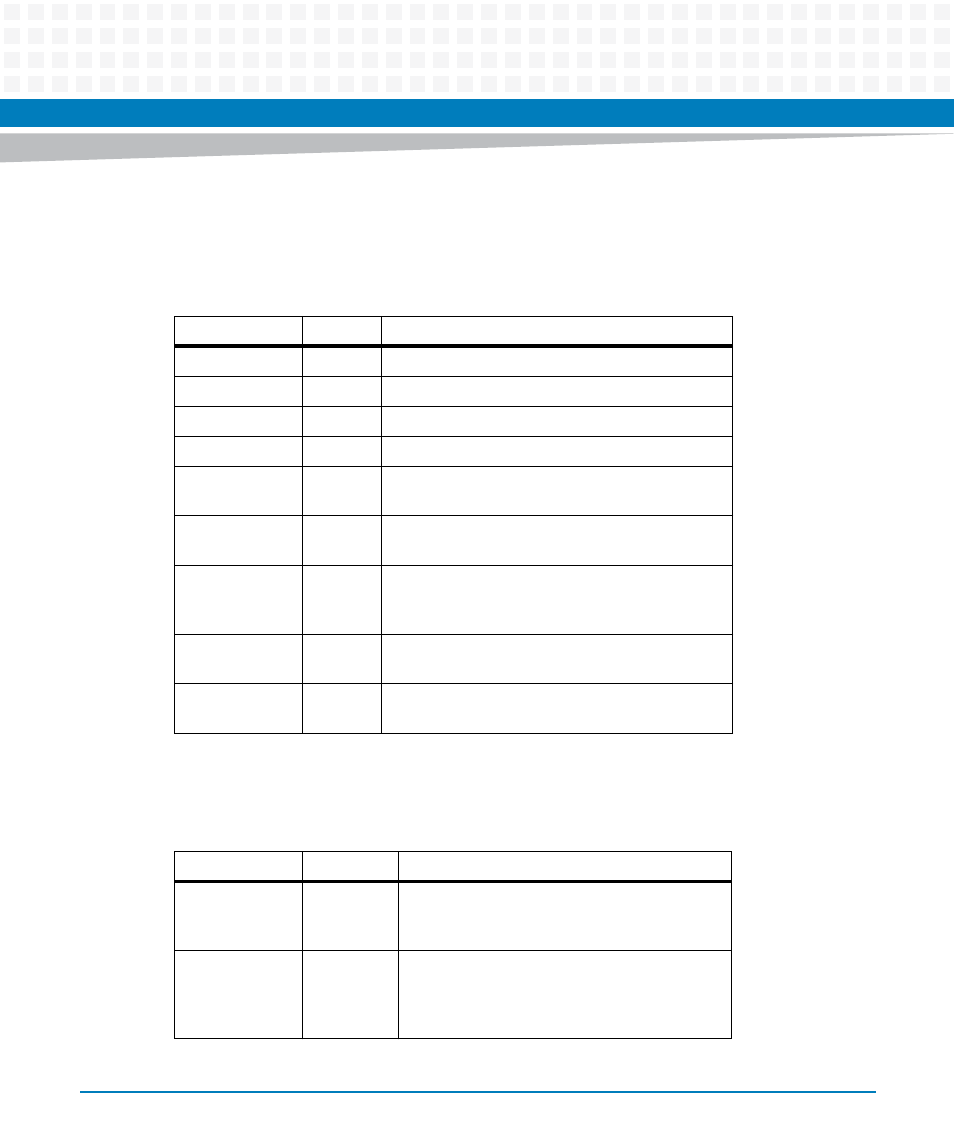

8.2.19 Configuration Signals

The Following Dual-Purpose Configuration Pins are used for SPI and SPIm modes.

Table 8-19 Dedicated Configuration Signals

Signal Name

Type

Description

TCK

I

JTAG clock

TMS

I

JTAG control

TDO

O

JTAG data out

TDI

I

JTAG data in

CCLK

O

Configuration Clock. Connected to

CONF_SPI_SCK.

DONE

O

Loading completion indication. Connected to

CPLD signal FPGA_DONE

INITN

O

Serial loading reset signal. If a CRC error is

detected during configuration INITN will be

driven low by the CPLD signal FPGA_INIT_

PROGRAMN

I

FPGA programming control input. Connected to

CPLD output FPGA_PROG_

CFG[2:0]

I

Configuration Mode Pins. 0b010: SPIm Mode.

Supports Golden and Working bit stream.

Table 8-20 Dual-Purpose Configuration Signals

Signal Name

Type

Description

DI/CSSPI0N

O

SPI chip select during configuration for SPI and

SPIm modes. In user mode used to generate

the SPI chip select signal CONF_SPI_SS_

D[7]/SPID0

I

SPI Master input Slave output during

configuration for SPIm mode, In user mode

used as input for SPI flash data. Signal

CONF_SPI_MISO