Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 211

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

211

Pwr = Power On Reset

Soft = Soft Reset

The TstPatCmp can be enabled to receive either static pattern or pseudo random pattern from

a remote generator.

In case of the Interior (Regs have indize 0) comparator it is connected to an outgoing timeslot

of the TSI.

In case of the Exterior (Regs have indize 1) comparator it is connected to an incoming timeslot

into the TSI.

The TSI timeslot is selectable between 0 and 65535.

The TstPatCmpBlk includes a PRBS pattern comparator (eleven stage LFSR with taps at the 9th

and 11th stage).

The pattern comparator is able to synchronize itself to the receive bit stream. After

synchronization 125 μs-frames and errors are counted.

A time of 125us delay has to be taken into account, till the comparator has stopped after

resetting TstPatCmpRxPatEn bit in TstPatCmpCtrlReg.

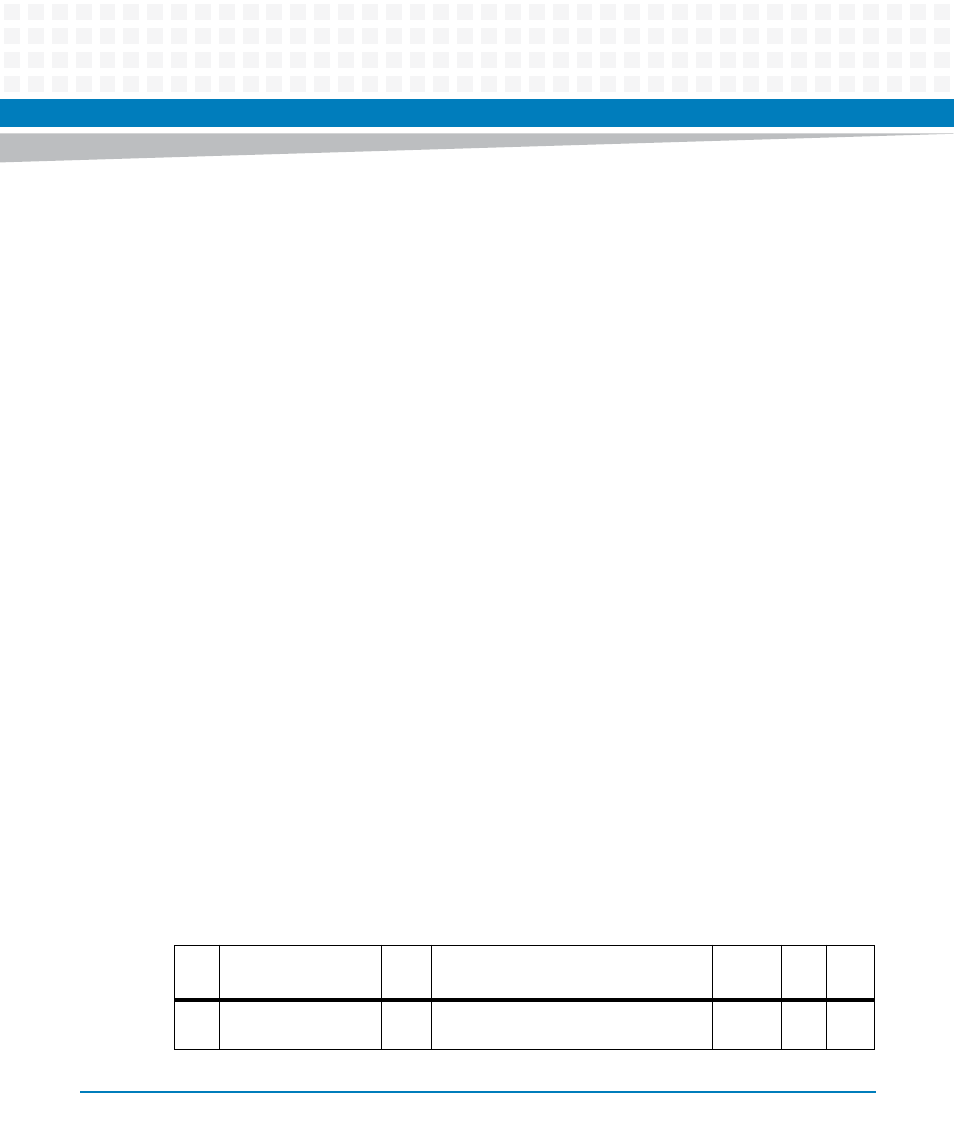

9.5.2.7.1 Test Pattern Comparator Timeslot Register

Addresses:

0x10C0, TstPatCmpTsReg0

0x10E0, TstPatCmpTsReg1

Width: 16 bit

This registers specifies the outgoing (Int) or incoming (Ext) TSI timeslot(0 ... 65535) to connect

the comparator to.

Bit

Acronym

Type

Description

Default

Pwr

Soft

15..

.0

TstPatCmpTsNo

RW

Selects the timeslot (0..65535) to

connect to.

0x0

X

X