Table 9-11, Pci revision id, Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 284

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

284

6

No user definable features

0

PCI: r

7

Device not capable of accepting Fast back-to-back transactions

when the transactions are not to the same agent.

0

PCI: r

8

Data Parity Error Detected. Not applicable for target device

0

PCI: r

10:9

DEVSEL Timing: Value of 0b10 indicates slow timing for DEVSEL_

assertion.

0b10

PCI: r

11

Signaled Target Abort

1: Target has terminated a transaction with Target Abort.

PCI_RST_

: 0

PCI:

r/w1c

12

Received Target Abort. Not applicable for target device.

0

PCI: r

13

Received Master Abort. Not applicable for target device.

0

PCI: r

14

Signaled System Error

1: The device has asserted SERR_

PCI_RST_

: 0

PCI:

r/w1c

15

Detected Parity Error

1: Device has detected a PCI bus parity error

This bit is set even if parity error handling is disabled (as controlled by

bit 6 in the Command register).

PCI_RST_

: 0

PCI:

r/w1c

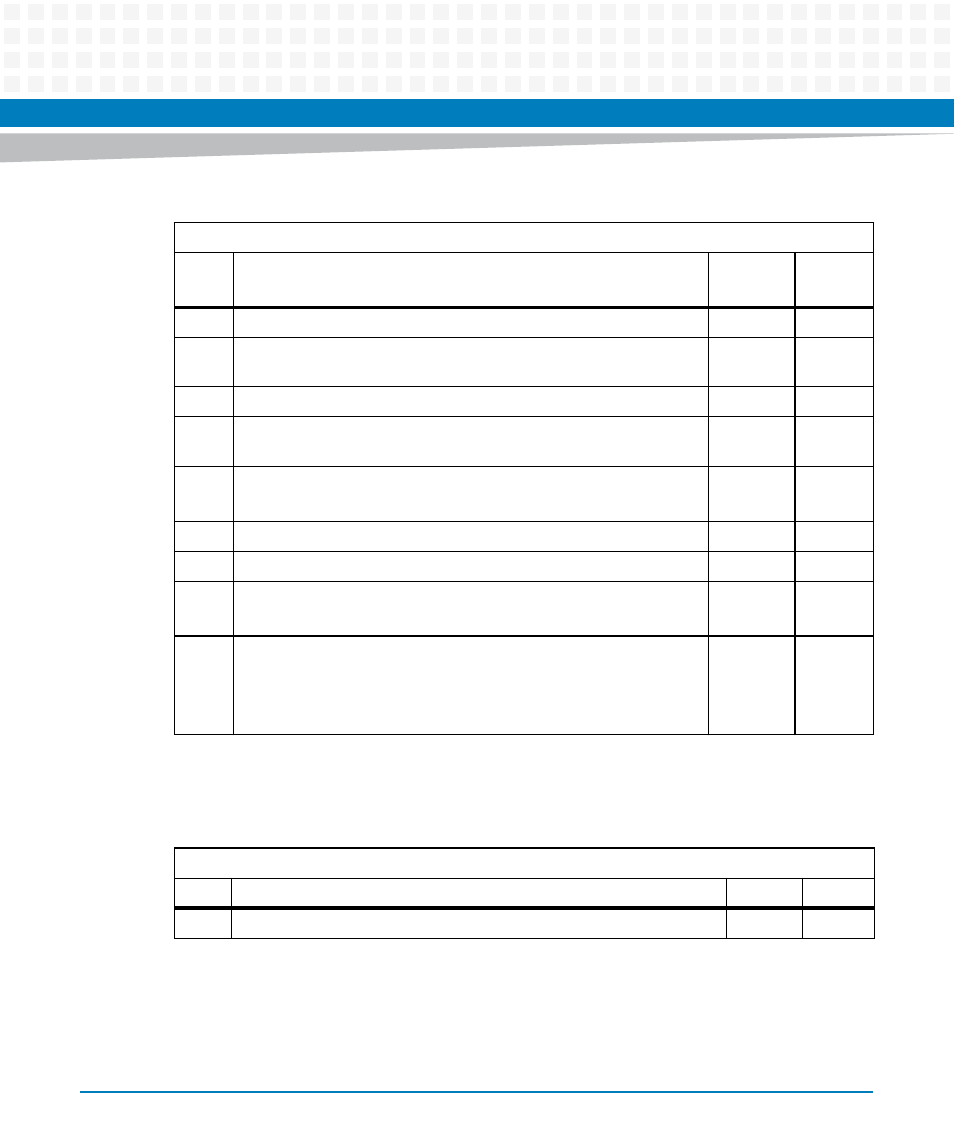

Table 9-11 PCI Revision ID

PCI Configuration Offset: 0x08

Bit Description

Default

Access

7:0

Revision ID. Start with 0. Incremented when PCI interface is updated.

0

PCI: r

Table 9-10 PCI Status (continued)

PCI Configuration Offset: 0x06

Bit

Description

Default

Access