Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 216

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

216

For static test pattern transmission a supplementary channel is provided. The supplementary

channel has a data rate of 128kbit/s because of the transmission of 16 bits every 125 μs.

Furthermore the Tsi2SerBlk controls the link synchronization and the CRC, Disparity insertion

of the SerDes IP Block.

9.5.2.8.1 Serdes Transmitter Control Register

Addresses:

0x1100, SerDesTrmCtrlReg0

0x1140, SerDesTrmCtrlReg1

0x1180, SerDesTrmCtrlReg2

Width: 8 bit

A Serdes transmitter reset or resync can be initiated via this register.

Reg0 is for Serdes-connection to the BaseBoard, Reg1 to DMC1 and Reg2 to DMC2.

9.5.2.8.2 Serdes Transmitter Status Register

Addresses:

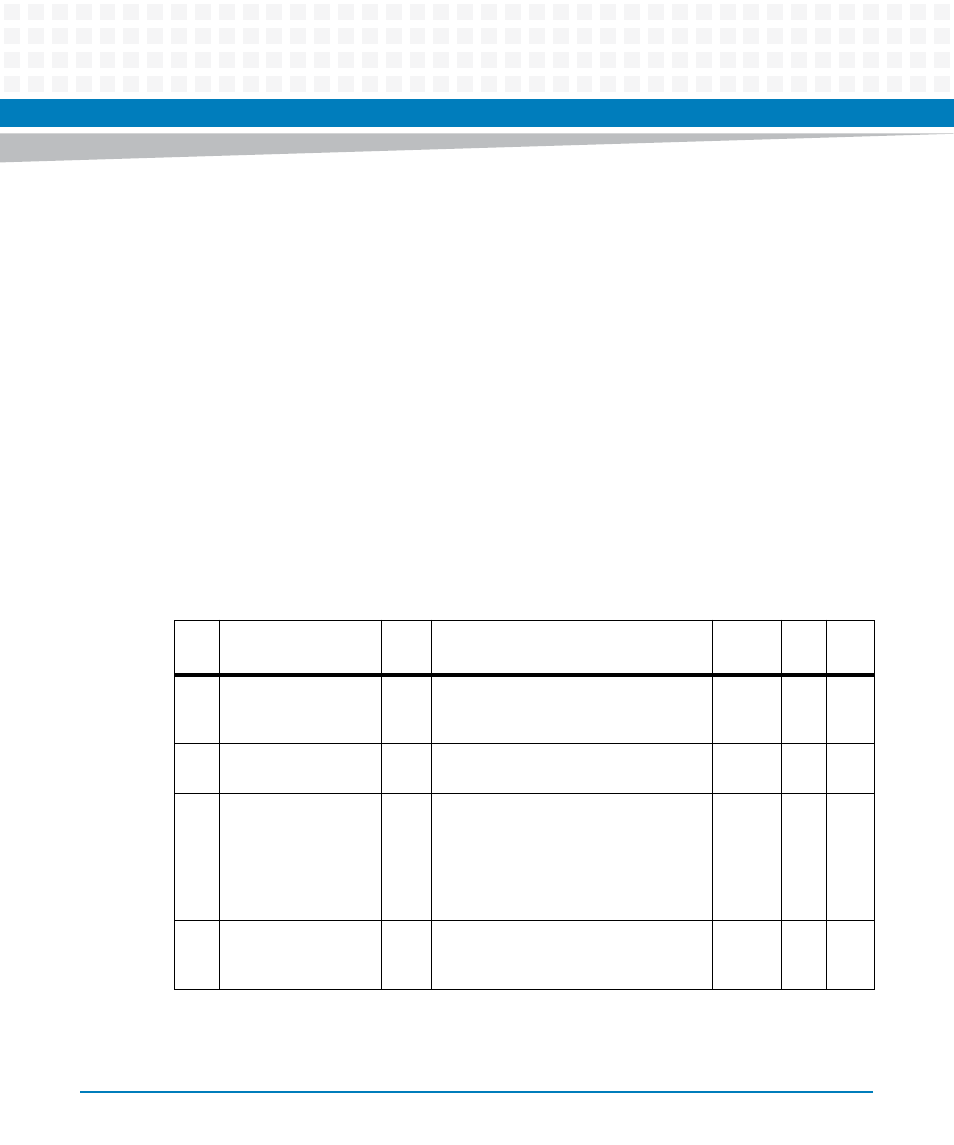

Bit

Acronym

Type

Description

Default

Pwr

Soft

7

SerdesTrmPllLolFlag

Reset

RW

0b1: SerdesTrmPllLolFlagReset, resets

the loss of lock flag bit in

SerDesTrmStatReg

0b0

X

X

6...

2

-

-

reserved

undef

-

-

1

SerdesTrmResync

RW

0b1: SerdesTrmResync, Serdes

transmitter sends resync pattern

sequence, 1 to 0 transition starts

sending of sequence, data is sent

automatically after the sequence has

ended

0b0

X

X

0

SerdesTrmReset

RW

0b1: SerdesTrmReset, puts the Serdes

transmitter into reset, resync sequence

is sent automatically when deactivated

0b0

X

X