1 artm base fpga code main-version, 2 sfp i2c select register, Table 8-25 – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 131: Artm base fpga code main-version, Table 8-26, Sfp i2c select register, Base artm fpga

Base ARTM FPGA

ARTM-831X Installation and Use (6806800M76E)

131

8.3.1.1

ARTM Base FPGA Code Main-Version

8.3.1.2

SFP I2C select Register

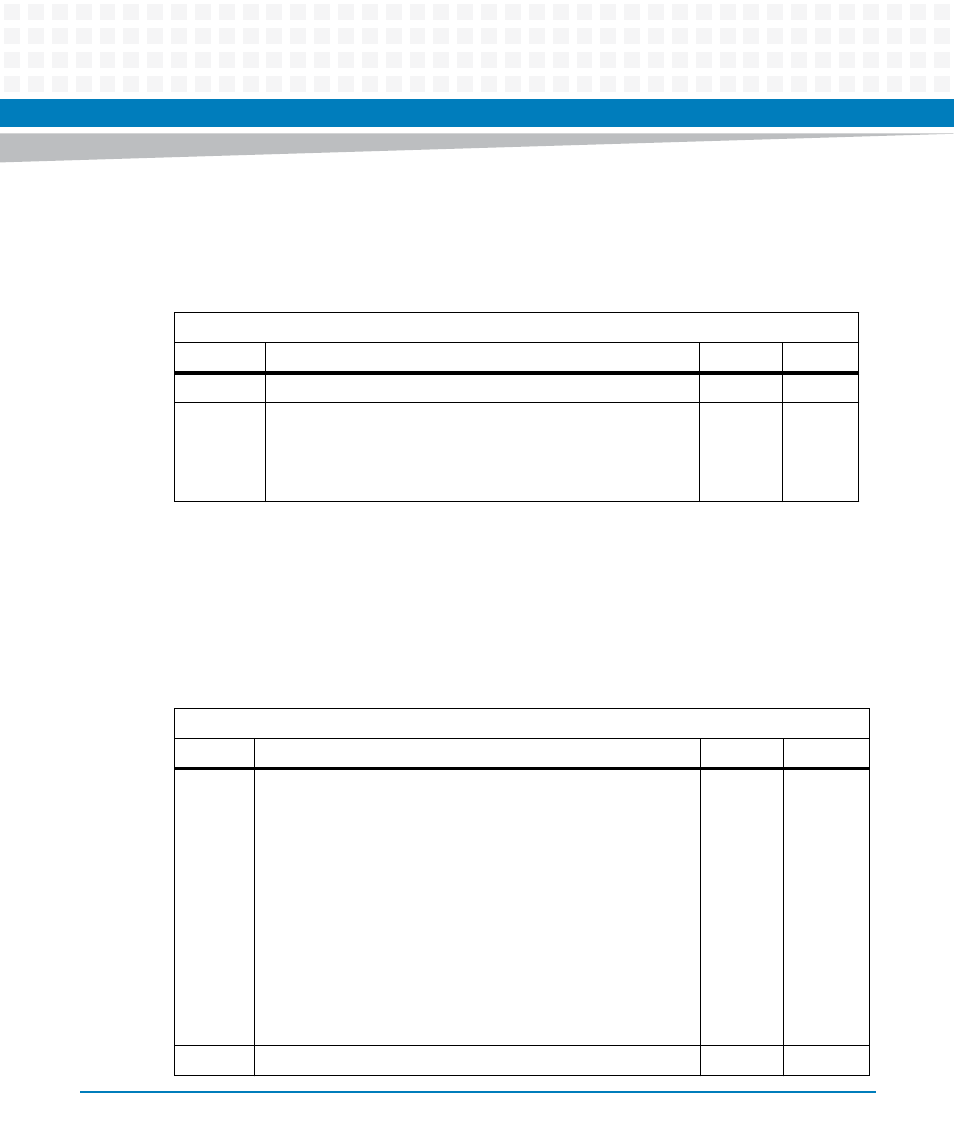

Table 8-25 ARTM Base FPGA Code Main-Version

Address: 0x0

Bit Description

Default

Access

6:0

FPGA Code Main-Version. Incremented with each new version. 1

r

7

FPGA Configuration image. Show currently loaded FPGA

image.

0: Working

1: Golden

0

r

Table 8-26 SFP I2C select Register

Address: 0x1

Bit Description

Default

Access

3:0

SFP I2C selection:

0x0: SFP 1 SONET Bus Signals I2C_SFP_SCL_1, I2C_SFP_SDA_1

0x1: SFP 2 SONET Bus Signals I2C_SFP_SCL_2, I2C_SFP_SDA_2

0x2: SFP 3 SONET Bus Signals I2C_SFP_SCL_3, I2C_SFP_SDA_3

0x3: SFP 4 SONET Bus Signals I2C_SFP_SCL_4, I2C_SFP_SDA_4

0x4: SFP 5 SONET Bus Signals I2C_SFP_SCL_5, I2C_SFP_SDA_5

0x5: SFP 6 SONET Bus Signals I2C_SFP_SCL_6, I2C_SFP_SDA_6

0x7: SFP 7 SONET Bus Signals I2C_SFP_SCL_7, I2C_SFP_SDA_7

0x7: SFP 8 SONET Bus Signals I2C_SFP_SCL_8, I2C_SFP_SDA_8

0x8: SFP+ 10G Bus Signals I2C_SFP_SCL_9, I2C_SFP_SDA_9

0x9 - 0xF: Reserved

0

MMC: r/w

6:4

Reserved

0

r