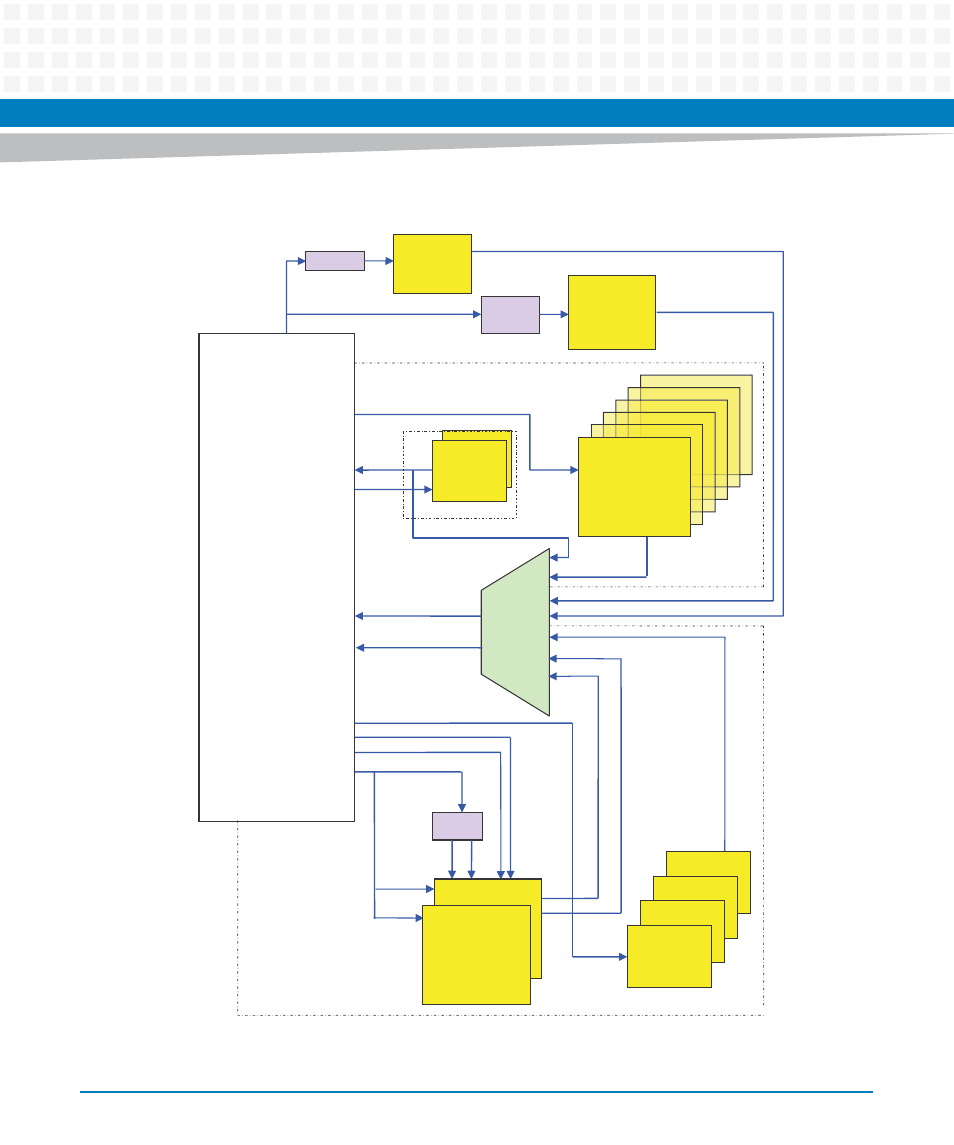

Figure 4-4, Artm-831x synchronous clock distribution, Functional description – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 64

Functional Description

ARTM-831X Installation and Use (6806800M76E)

64

Figure 4-4

ARTM-831X Synchronous Clock Distribution

PLL ICS

81332202

155M52

SONET/SDH OC12

PM8310

SYSCLK

SYSCLK

2kHz/166.7Hz

Zone 3 connector

TSI unit & TSI extender FPGA’s:

Receive or generates

TDM/syncETH clocks from

eSETS PLL:

¾ 77.76 MHz

¾ 32.768 MHz

¾ 25MHz

¾ 16.384 MHz

¾ 12.288 MHz

¾ T4

¾ 8

kHz

¾ 2

kHz

¾ 166.666 Hz

Return TDM/syncETH clocks:

¾ T3

¾ RefCLK 1,2

¾

166.666 Hz (to update

channel)

16M384 H-MVIP

Recovered

clock select

25MHz

10GBE

BCM8707

1…48 channel E1/T1

octal E1/T1

Expansion board

Base board

T3

1M544

2M048

BITS DS26503

BITS DS26503

T4

1M544

2M048

Located on base board

48x

1M544

2M048

PLL-813N252

156M25

4x 1GB Eth

BCM54640

PLL-810251

156M25

2x 25MHz

2x 125MHz

12M288

8kHz

Hex E3/DS3/

STS-1 LIU

Hex E3/DS3/

STS-1 LIU

Hex E3/DS3/

STS-1 LIU

RefCLK 1

RefCLK 2

8x

19M44

77M76

8x

1M544

2M048

24x

34M368

44M736

51M84

77M76

Hex E3/DS3/

STS-1 LIU

SONET/SDH OC12

PM8310