Base artm fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 130

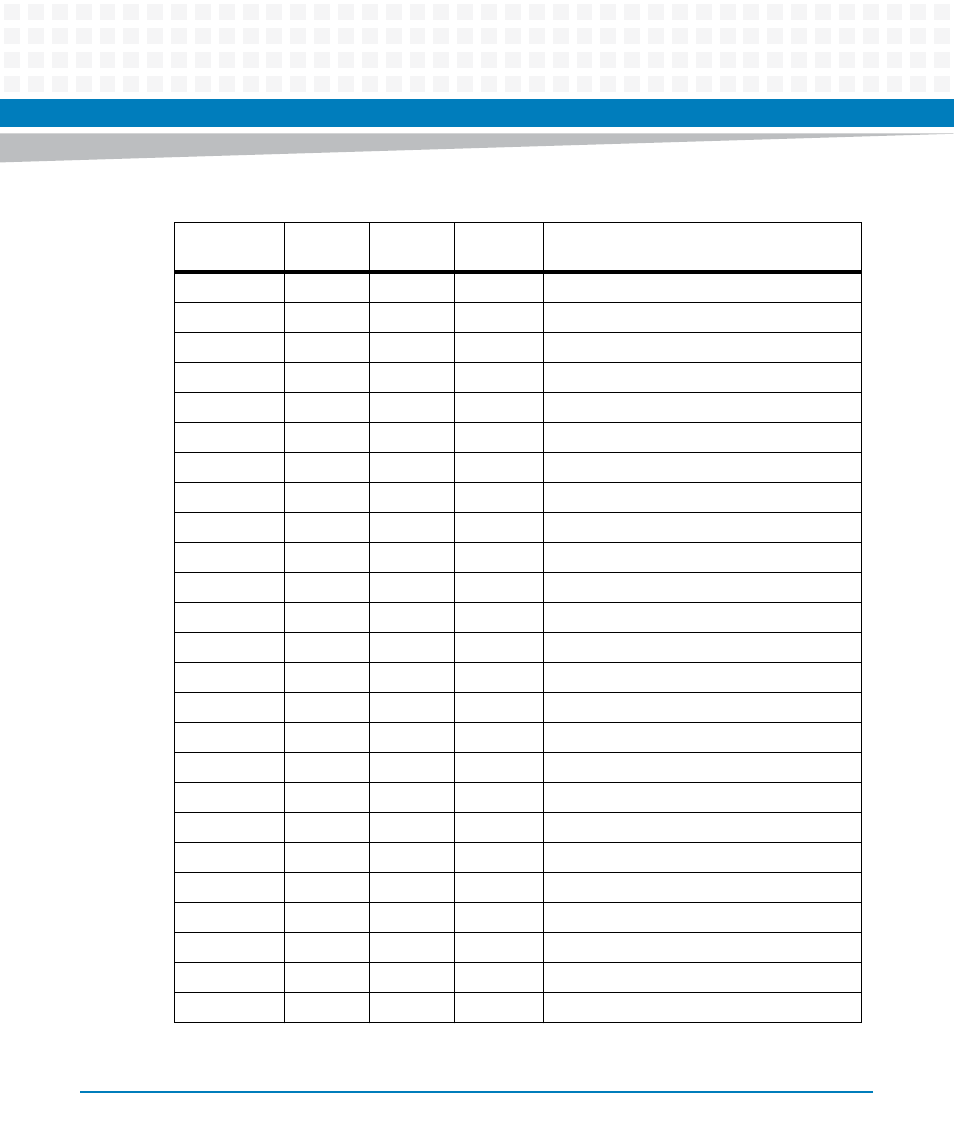

Base ARTM FPGA

ARTM-831X Installation and Use (6806800M76E)

130

0x2

x

x

x

ARTM Base FPGA Code Sub-Version

0x3

x

x

SFP TXFAULT Status

0x4

x

x

SFP MOD_ABS Status

0x5

x

x

SFP TXDIS Control

0x6 - 0x7

x

x

10 GE Status Register

0x8

x

x

10 GE Control Register

0x9

x

x

MMC Scratch Register

0xA

x

x

RTM Scratch Register

0xB

x

x

x

Telecom Reference Clock Selection

0xC

x

x

GE Control Register

0xD

x

Force CRC Error Register

0xE

x

x

Test Register

0xF

x

x

Other Status Signals Register

0x10

x

SFP TXFAULT Level Changed

0x11

x

SFP TXFAULT interrupt enable

0x12

x

SFP MOD_ABS changed

0x13

x

SFP MOD_ABS interrupt enable

0x14 -0x15

x

10 GE Status changed

0x16-0x17

x

10 GE Status interrupt enable

0x18-0x1B

x

x

x

Telecom Reference Clock Divider Registers

0x1C

x

Interrupt Group Status

0x1D

x

x

x

Identification Register

0x1E - 0x1F

x

FPGA Code SPI Update Registers

0x20 - 0x2B

x

ARTM Telecom Clock Monitor Registers

0x30

x

x

ARTM Ethernet Reset Control Register

Table 8-24 ARTM Base FPGA Register Overview (continued)

Address /

Range

RTM SPI

SPI Mezz

MMC I2C

Description