Altera DDR Timing Wizard User Manual

Page 11

Altera Corporation

1–5

November 2007

DDR Timing Wizard User Guide

About the DDR Timing Wizard

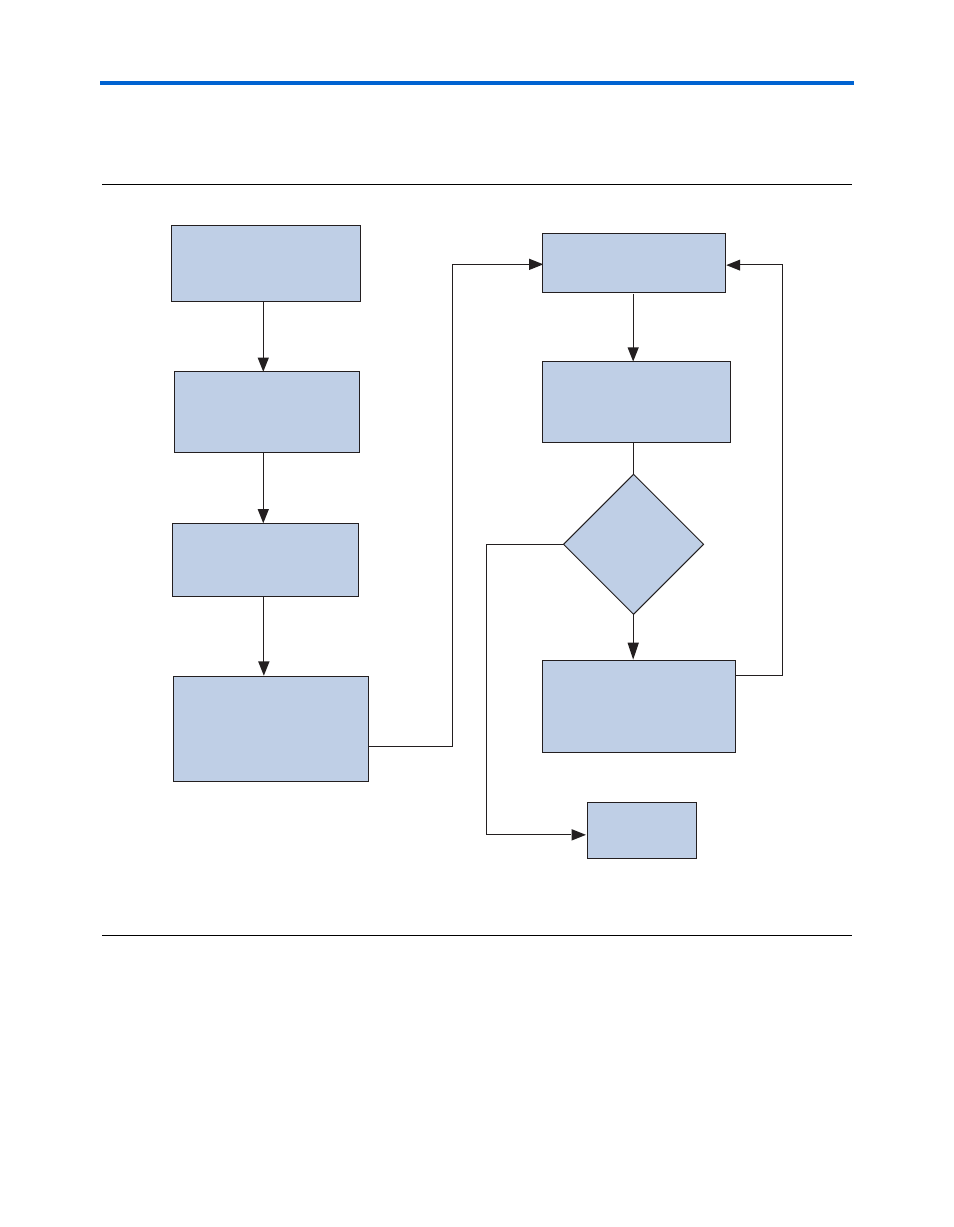

shows the typical Quartus II external memory design flow

using DTW and the dtw_timing_analysis.tcl script.

Figure 1–1. Quartus II External Memory Design Flow

Note to

:

(1)

It may be necessary to modify the controller and PHY settings (such as the clock cycles and clock phase shifts) using

the legacy controller or the altpll MegaWizard, based on dtw_timing_analysis.tcl results.

This user guide explains how to constrain designs using DTW, how to

analyze the memory interface timing using the dtw_timing_analysis.tcl

script, and how to adjust design constraints using the MegaWizard, the

Assignment Editor, or DTW to achieve timing closure.

Adjust Constraints

Using the MegaWizard,

the Assignment Editor,

or the DTW

Instantiate PHY

and Controller in a

Quartus II Project

Compile Design

Yes

Done

Run add_constraints.tcl

(Pin Locations,

I/O Standards, and Loading)

Run DTW

(Timing Constraints)

Run dtw_timing_analysis.tcl

to Get Margin and

Recommended Settings (1)

Add Assignments for Clock,

Command, and Address Pin

Locations, and Other Pertinent

Assignments for the Interface

No

Is

Memory

Interface Timing

Met?