Altera DDR Timing Wizard User Manual

Page 62

3–2

Altera Corporation

DDR Timing Wizard User Guide

November 2007

Introduction

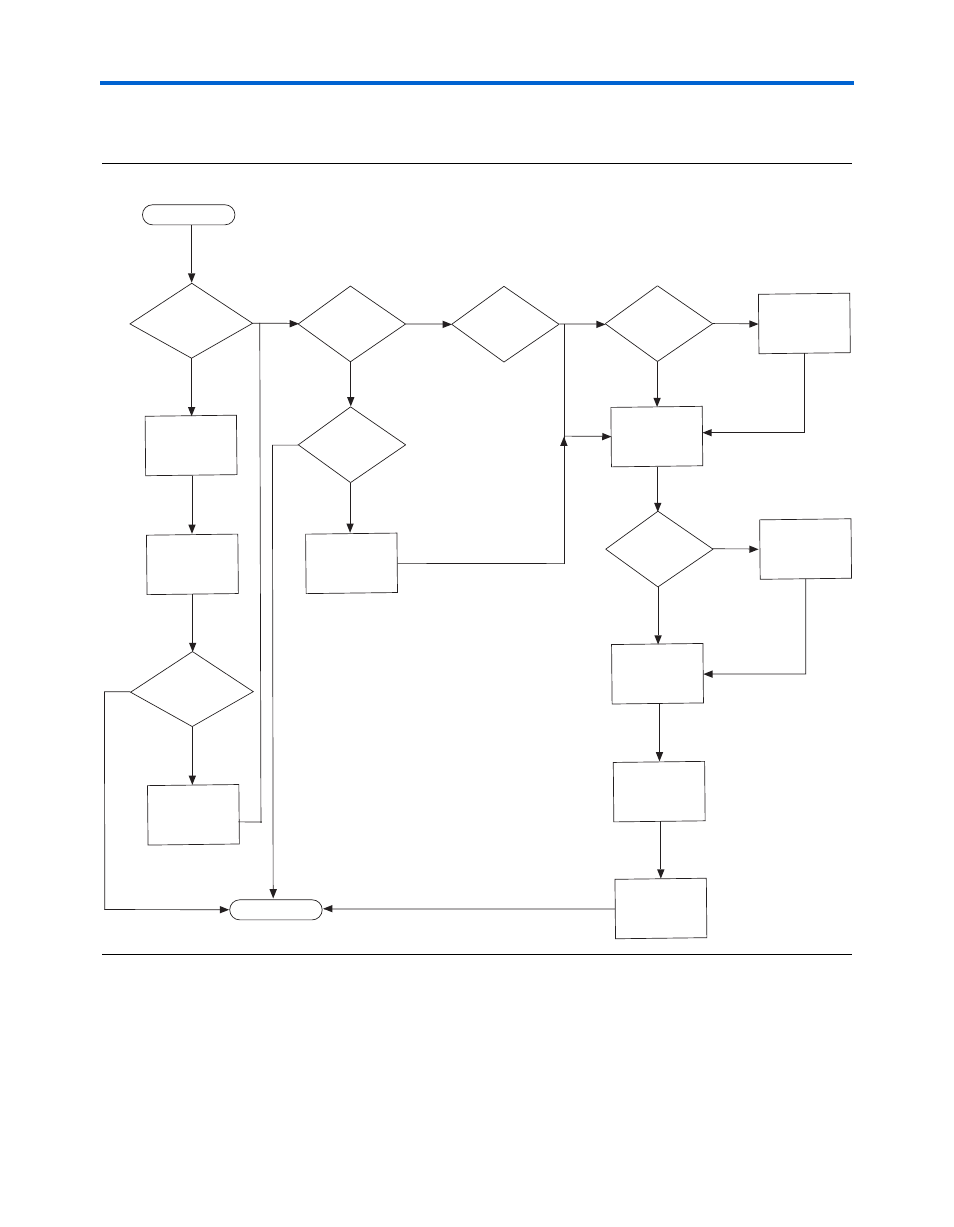

shows the general algorithm of the dtw_timing_analysis.tcl.

Figure 3–1. The dtw_timing_analysis.tcl algorithm

Extract design

tcos and apply

tcos to DTW

Start

Yes

No

Done

Is —after_iptb

set to import or

import_and_compile?

Is

—auto_adjust_cycles

used?

Is

—extract tcos

set to Ignore?

Does DTW

tcos match with

design tcos?

Is any of the

margin bigger than

one clock period?

DTW is set

to both fast and slow

model design

tcos

Analyze and

Elaborate the

design

Import the new

settings to DTW

Compile the design

Rerun DTW with

the recommended

clock cycles

Get timing margin

for slow model

Get timing margin

for fast model

Calculate ideal

phase shift

Display margin and

phase shift

recommendations

Rerun DTW for fast

model and perform

timing analysis for

fast model

Is —after_iptb

set to

import_and_compile?

Yes

Yes

Yes

Yes

Yes

No

No

No

No

Yes

No

Yes

No