Adjusting clock cycle selections – Altera DDR Timing Wizard User Manual

Page 85

Altera Corporation

3–25

November 2007

DDR Timing Wizard User Guide

Using the dtw_timing_analysis.tcl Script

ii. Open the altpll MegaWizard to modify the

rldramii_pll_stratixii.v/.vhd

and change the clock phase

shift of the c2 output clock accordingly.

The altpll may not be able to give you the exact phase

shift due to the PLL configuration, but it will give you the

closest phase shift to the one that you set in either

MegaWizard.

1

Whenever you make a change in the MegaWizard or the

RTL files, peform an Analysis and Synthesis on the design

before reimporting the settings into DTW.

Adjusting Clock Cycle Selections

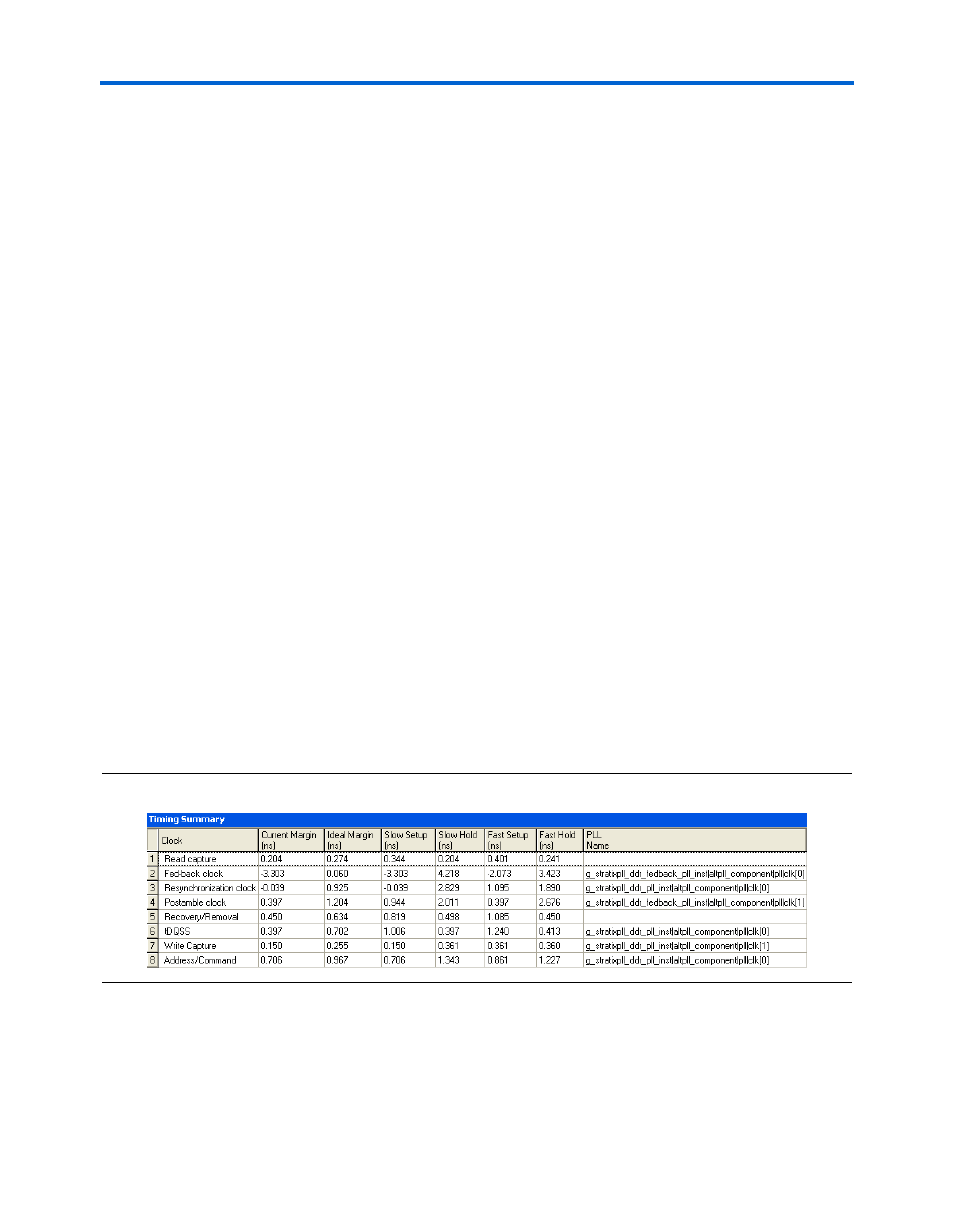

A timing margin (either positive or negative) of more than one clock

period in the Timing Summary panel indicates that one of the clock cycle

selections in the DTW is incorrect. However, it does not necessarily mean

that you need to change the clock cycle of this particular clock listed in the

Timing Summary

panel. The dtw_timing_analysis.tcl script analyzes

the timing of the whole interface and may find that you need to adjust the

clock cycle of the clock downstream from the clock listed in the Timing

Summary

panel.

For example,

Figures 3–12

shows a current margin of -3.303 ns for the

fedback clock for a 267-MHz DDR2 SDRAM design. However, if you look

under the Slow Hold column, the fedback clock has a positive margin of

4.218 ns. This indicates that the clock arrives one clock cycle too late. In

, dtw_timing_analysis.tcl suggests that you need to add one

clock cycle to the resynchronization clock, and not the fedback clock.

Figure 3–12. Timing Summary Example with <1 Clock Cycle Margin