Altera DDR Timing Wizard User Manual

Page 44

2–32

Altera Corporation

DDR Timing Wizard User Guide

November 2007

Entering and Editing Inputs to the DTW

shows the relationship between the legacy controller

MegaWizard and the DTW in terms of postamble clock cycles and

phase shifts. This relationship for a 2-PLL mode example is also

shown in

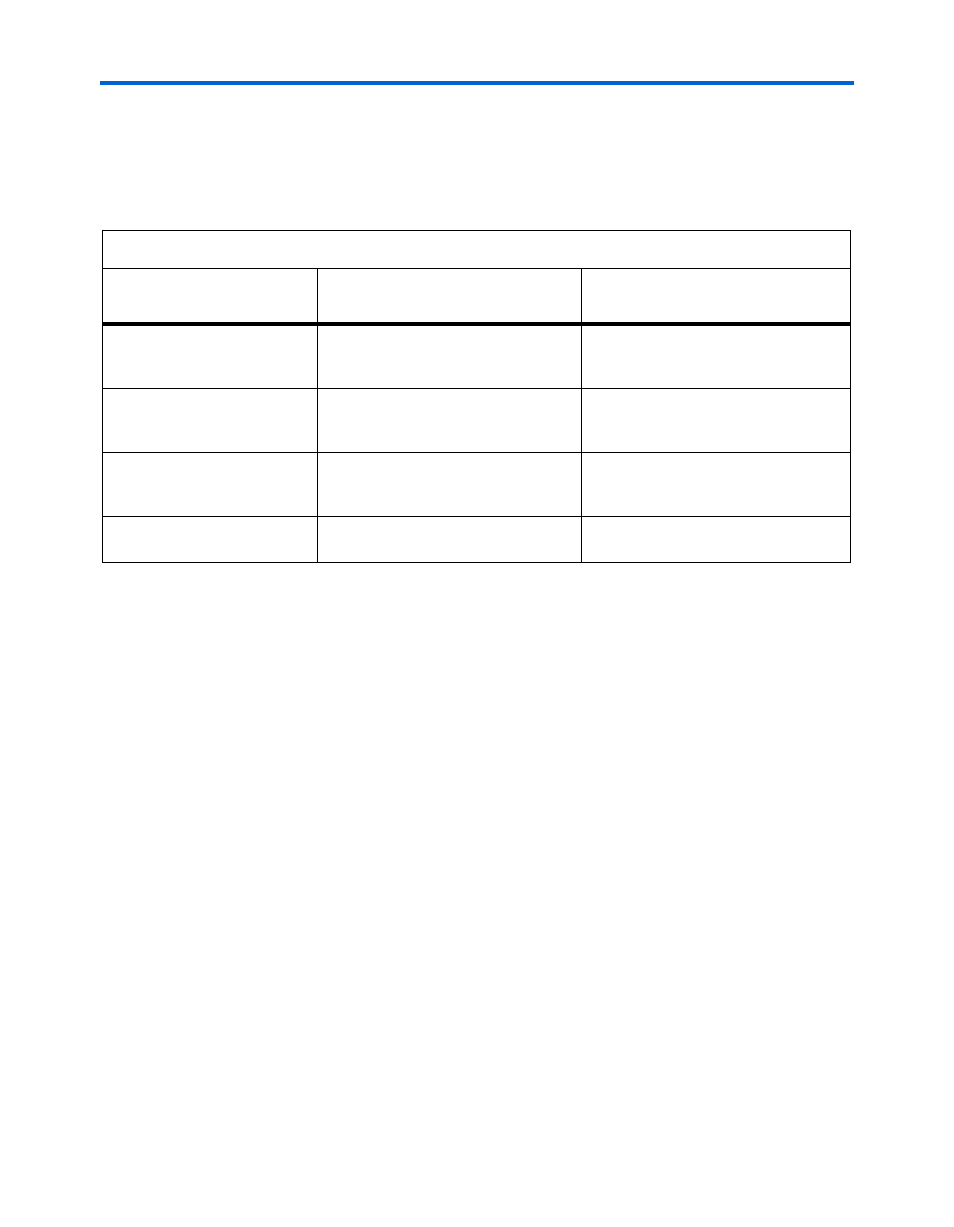

Table 2–2. Relationship Between the Legacy Controller MegaWizard and the DTW

DTW Postamble Fields

Interfaces with One PLL

(

≤

200 MHz)

Interfaces with Fedback-Clock Mode

(> 200 MHz)

postamble_cycle

From the Postamble cycle field in the

legacy controller MegaWizard Manual

Timings tab

Calculated by DTW

postamble_phase

From the Dedicated clock phase

field in the legacy controller

MegaWizard Manual Timings tab

From the Dedicated clock phase field

in the legacy controller MegaWizard

Manual Timings tab

postamble_sys_cycle

Not used

From the “Postamble cycle” field in

the legacy controller MegaWizard

Manual Timings tab

postamble_sys_phase

Not used

0° or -180° whether intermediate

postamble registers are used or not.

Note to

:

(1)

For new designs targeting memory interfaces higher than 200 MHz, Altera recommends using the

high-performance controller featuring the ALTMEMPHY megafunction in the Quartus II software.