S, you can either use the – Altera DDR Timing Wizard User Manual

Page 78

3–18

Altera Corporation

DDR Timing Wizard User Guide

November 2007

Timing Closure Process

and hold time requirements of the user logic clocked by the system clock.

The ideal phase shift may change by a few degrees, due to

place-and-route changes due to the register insertion.

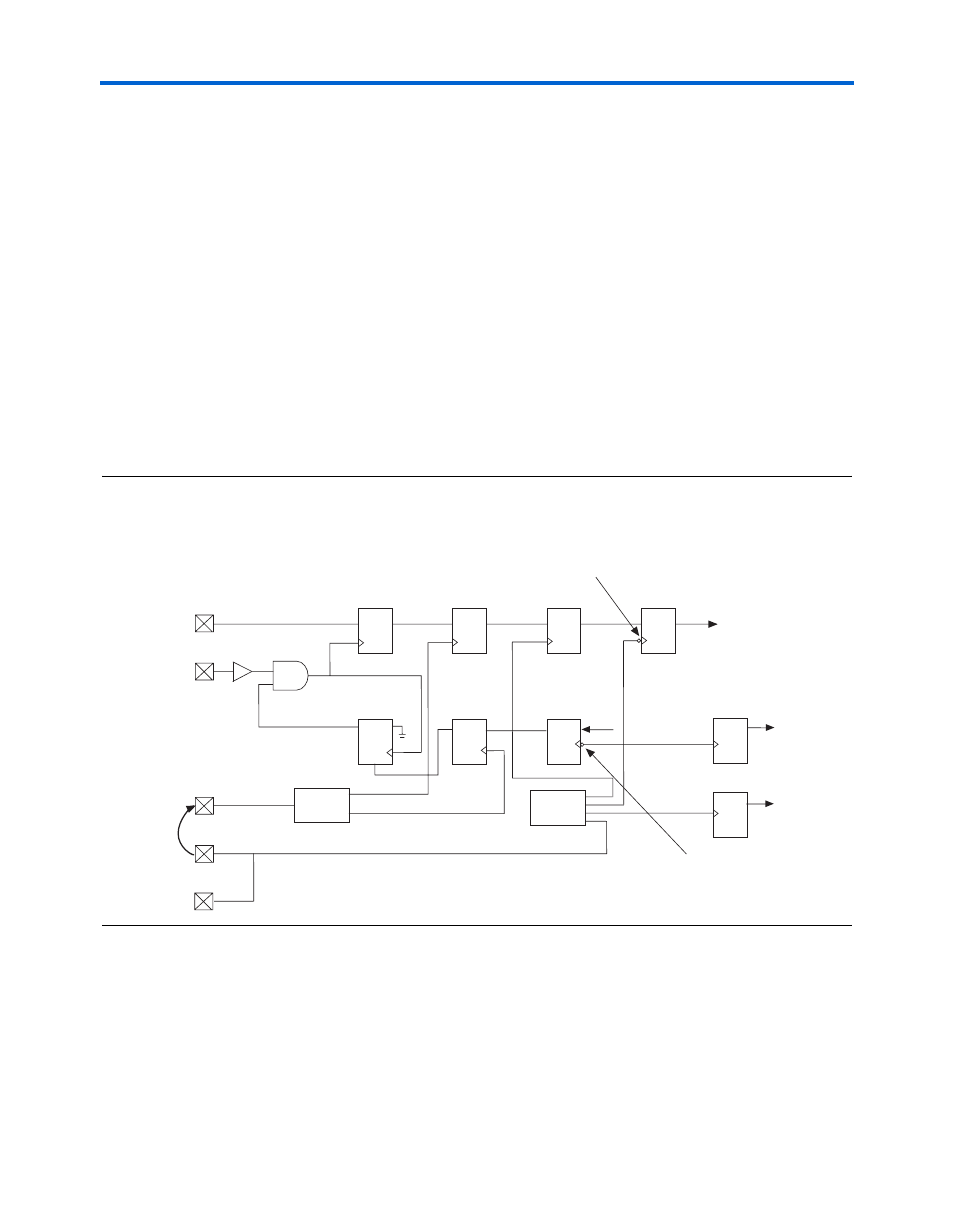

The intermediate postamble registers, on the other hand, affects the

postamble clock cycle and phase shift selections. When the Intermediate

postamble registers

option is unchecked, the clock going to the system

postamble registers is the system clock inverted by 180°. When that

option is checked, the clock going to the system postamble registers is the

0° system clock. Therefore, the state of this option affects the clock phase

shift of the dq_enable_reset registers.

Figures 3–9

shows the relationships of the resynchronization registers

and postamble registers with their respective intermediate registers for

fedback-PLL mode interfaces in Stratix II devices. The name of the

registers shown are from the DDR2 SDRAM Controller Compiler names.

Figure 3–9. Resynchronization, Postamble, and Intermediate Registers Connections for Fedback-PLL mode

in Stratix II Devices

Re-run DTW After First Compile When Using Classic Timing

Analyzer

For any memory interfaces using Classic Timing Analyzer, you need to

extract the design t

CO

to the DTW after the first compile and then run the

dtw_timing_analysis.tcl

script. To extract t

CO

s, you can either use the

D Q

Fedback

PLL

D Q

D Q

D Q

D Q

D Q

System

PLL

Q D

Q D

Q D

dq_capture

resynched_data

fedback_

resynched_data

inter_rdata

User logic

dq_enable_reset

doing_rd_delayed

dq

dqs

DQ

DQS,

CK/CK#, Address,

Command,

Fedback out

User logic

Optional, depending on setting

of "Insert intermediate

resynchronization registers"

Optional, depending on setting

of "Insert intermediate

postamble registers"

Fedback

clock in

Optional

Fedback

clock out

Optional CK/CK#

clk1

clk0

clk2

clk0

clk3

clk1

First

Resynchronization

Registers

Second

Resynchronization

Registers

Intermediate

Resynchronization

Registers

Postamble

System Postamble