Changing clock cycles – Altera DDR Timing Wizard User Manual

Page 87

Altera Corporation

3–27

November 2007

DDR Timing Wizard User Guide

Using the dtw_timing_analysis.tcl Script

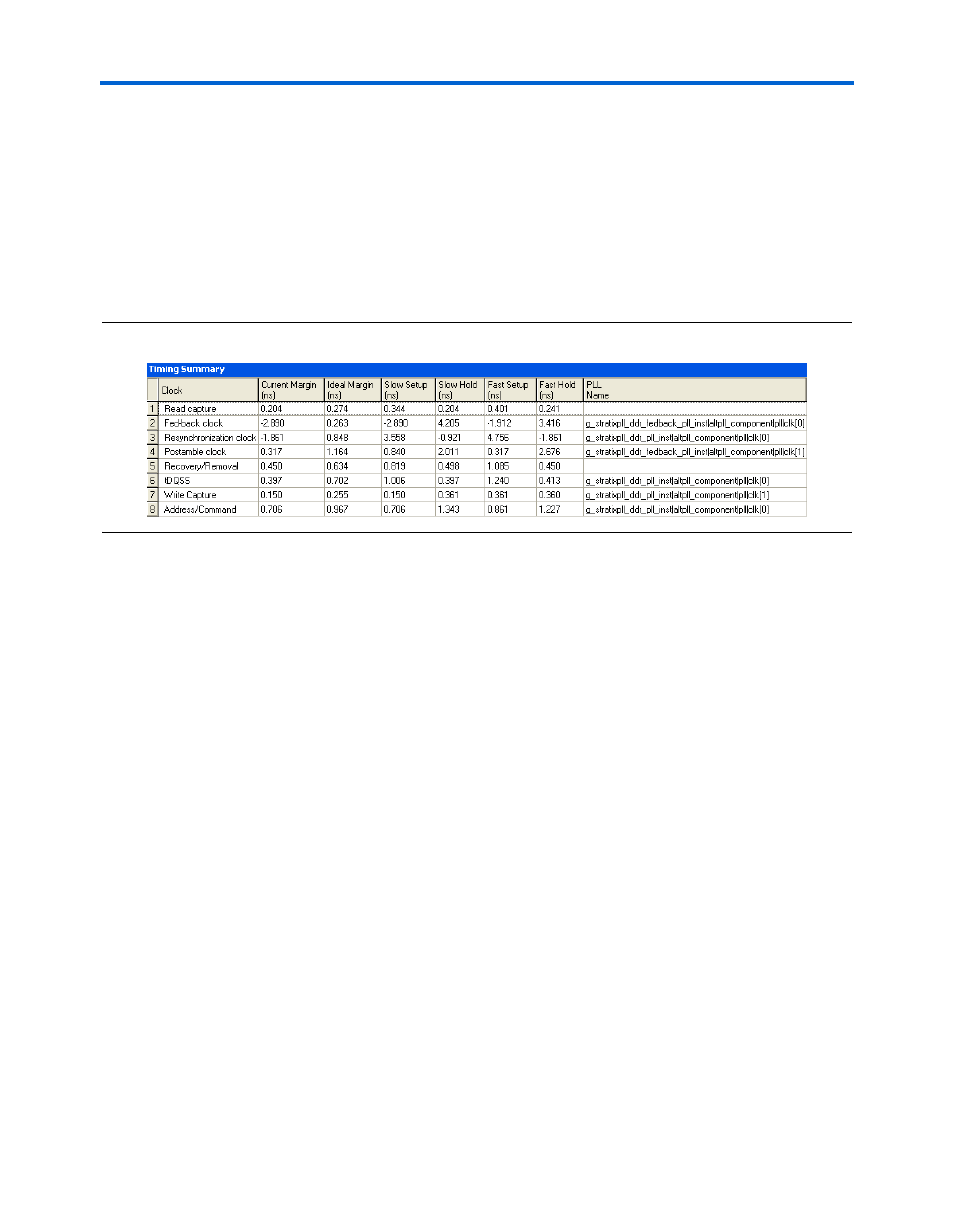

You can then use the -auto_adjust_cycles switch to see what the

predicted margin is after you change the clock cycle of the

resynchronization clock. The Timing Summary panel from the following

command is shown in

Figure 3–14

:

quartus_sh -t

c:\altera\72\quartus\common\tcl\apps\gui\dtw\

dtw_timing_analysis.tcl -dwz_file ddr_settings.dwz

-auto_adjust_cycles

Figure 3–14. Predicted Margin after Adjusting Clock Cycle Selection

When you use the -auto_adjust_cycles switch, the

dtw_timing_analysis.tcl

script changes the clock cycles in the DTW per

the previously-ran results. You cannot go back to the clock cycle

selections used in the compilation unless you re-import the settings into

DTW.

Changing Clock Cycles

This is applicable to DDR2/DDR SDRAM interfaces only.

The clock cycles determine when data should be resynchronized or when

the DQS postamble control needs to be asserted. The MegaWizard has

one clock cycle selection each for resynchronization and postamble paths,

regardless whether it is a 1-PLL or 2-PLL implementation mode. This

clock cycle selection always pertains to the path that is crossing the

system clock domain, for example from the second resynchronization

clock to the system clock domain. You can change the clock cycle in the

Manual Timings

page in the Parameterize section of the legacy

controller.

f

Clock Cycle 0 begins from the first rising edge of the system clock after

the first rising edge of the DQS signal, assuming a CAS latency of 3. For

more information, refer to Appendix A. Manual Timing Settings of the

.