Figure 2–27, Show the fpga pa – Altera DDR Timing Wizard User Manual

Page 50

Advertising

2–38

Altera Corporation

DDR Timing Wizard User Guide

November 2007

Entering and Editing Inputs to the DTW

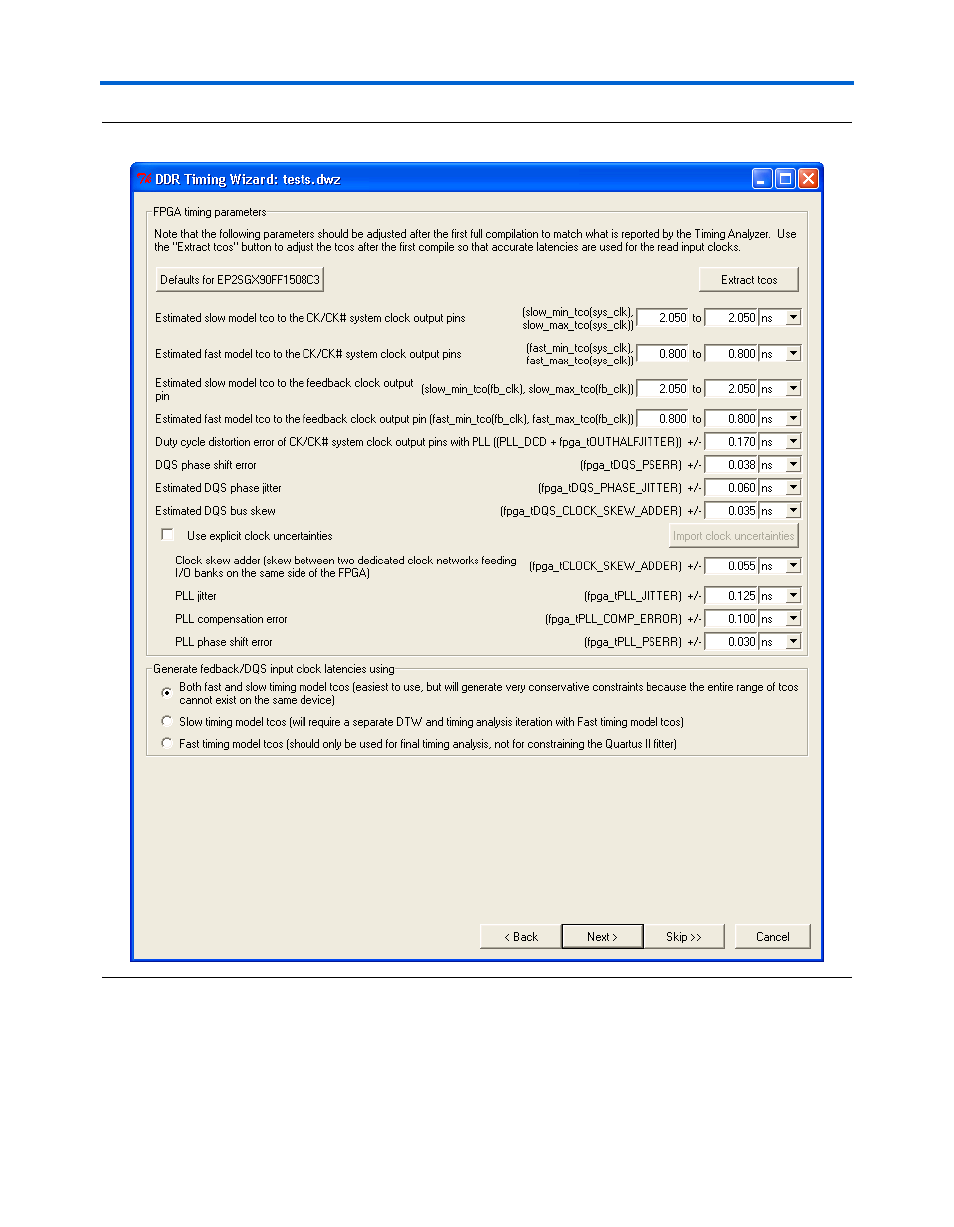

Figure 2–27. FPGA Timing Parameters Page When Using Classic Timing Analyzer Names

Use the Use explicit uncertainties option in lieu of the separate clock

skew adder, PLL jitter, compensation error, and phase shift error

when targeting a HardCopy II device. These numbers were

characterized for the FPGA and are included in the timing model,

Advertising