Altera DDR Timing Wizard User Manual

Page 86

3–26

Altera Corporation

DDR Timing Wizard User Guide

November 2007

Timing Closure Process

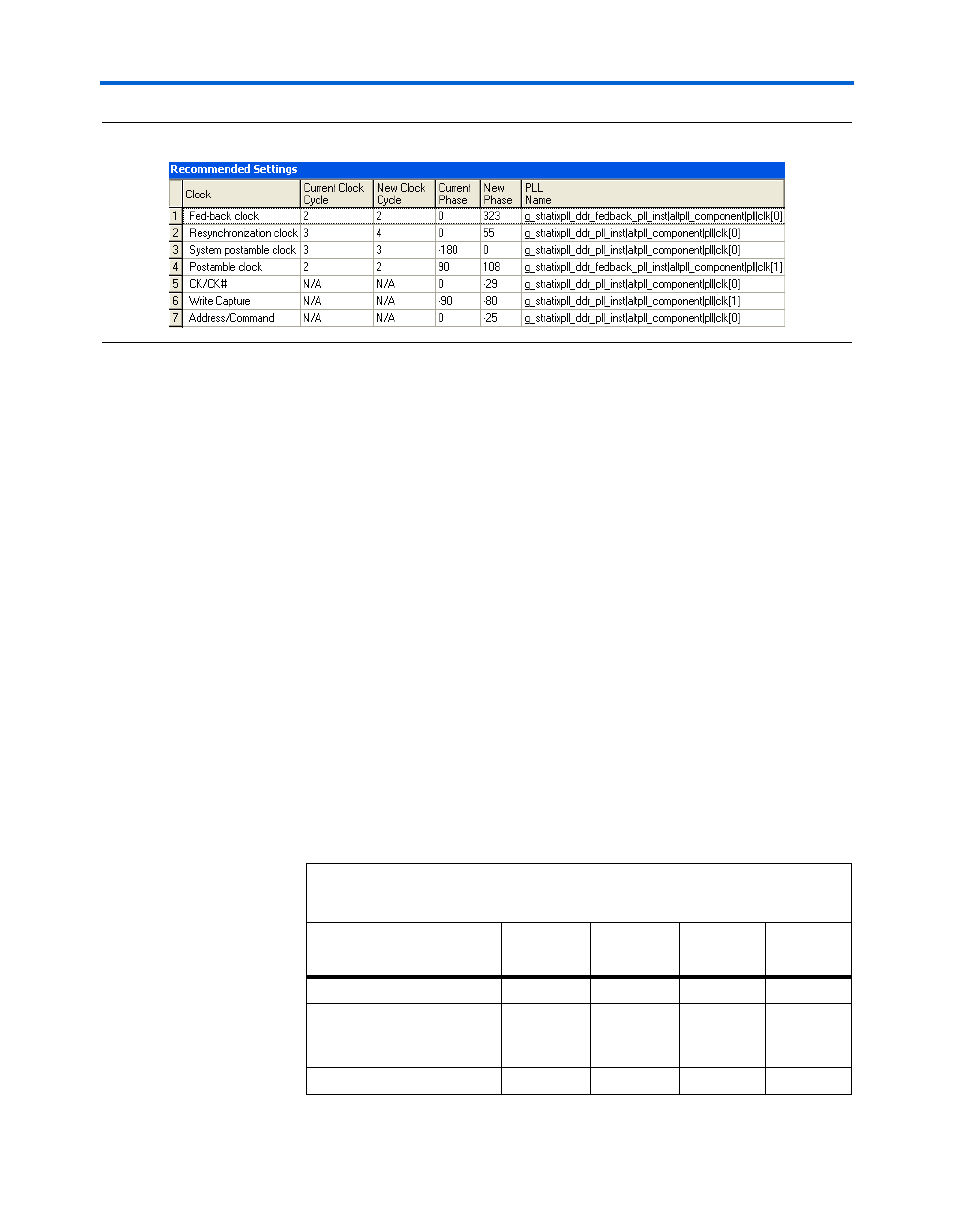

Figure 3–13. Recommendation Setting To Change Clock Cycle Selection

This is because the dtw_timing_analysis.tcl script calculates an ideal

margin of 263 ps for the fedback clock. In order to get this margin, peform

the following calculation:

Phase shift to get ideal fedback clock margin:

Ideal fedback clock margin = (ideal margin - current margin)/ clock

period × 360

°

= (263 - (-2.890))/3.750 × 360

°

= 303

°

Pushing the fedback clock phase shift means that the data clocked by the

resynchronization clock is also pushed by the same amount. The resultant

margin after the push is shown in

Table 3–5

, which displays margin of

over one clock period. This justifies the dtw_timing_analysis.tcl

recommendation in the Recommended Settings to adjust the clock cycle

for the resynchronization clock instead of the fedback clock.

1

This also shows the power of the dtw_timing_analysis.tcl script

since it analyzes the ideal timing for the whole interface instead

of for one clock at a time. This cuts down the number of

recompilations for timing closure.

Table 3–5. Resultant Resynchronization Margin after Fedback Clock Phase

Shift Adjustment

Slow Setup

(ns)

Slow Hold

(ns)

Fast Setup

(ns)

Fast Hold

(ns)

Margin from compilation

-0.192

2.829

1.006

1.889

Add 330° (from fedback

clock phase shift

adjustment)

3.153

3.153

3.153

3.153

Resultant margin

2.961

5.982

4.159

5.042