Device family support, Introduction, Background – Altera DDR Timing Wizard User Manual

Page 8: Device family support –2 introduction –2

1–2

Altera Corporation

DDR Timing Wizard User Guide

November 2007

Device Family Support

Device Family

Support

The DTW Tcl script provides full support for the target Altera device

families and memory interfaces listed in

. In Quartus II software

version 6.0 SP1, the dtw_timing_analysis.tcl script was created to

supplement DTW. The dtw_timing_analysis.tcl script supports the same

device family and external memory interface combinations as the DTW.

Introduction

External memory interfaces have timing requirements that must be met

for both the FPGA and the memory devices. Some timing requirements,

such as controller f

MAX

, can be analyzed by the Quartus II software and

easily met, but some timing requirements need further analysis or

manual handling. To meet these timing requirements, you should

constrain the placements of the registers or specify timing constraints for

the Quartus II software to optimize during compilation.

Background

Previously, the legacy controller MegaWizard generated a script to

constrain critical registers for the system called

auto_add_ddr_constraints.tcl

. This script was used with the

verify_timing.tcl

script, which was run to verify the system timing based

on these constraints. The verify_timing.tcl script, however, made some

assumptions that may not have been true for your design. For example,

the verify_timing.tcl script assumed that all clocks used for the memory

interface were using the global clock networks, so if you used a regional

clock network, some of the timing reported by the verify_timing.tcl

script may not have been accurate.

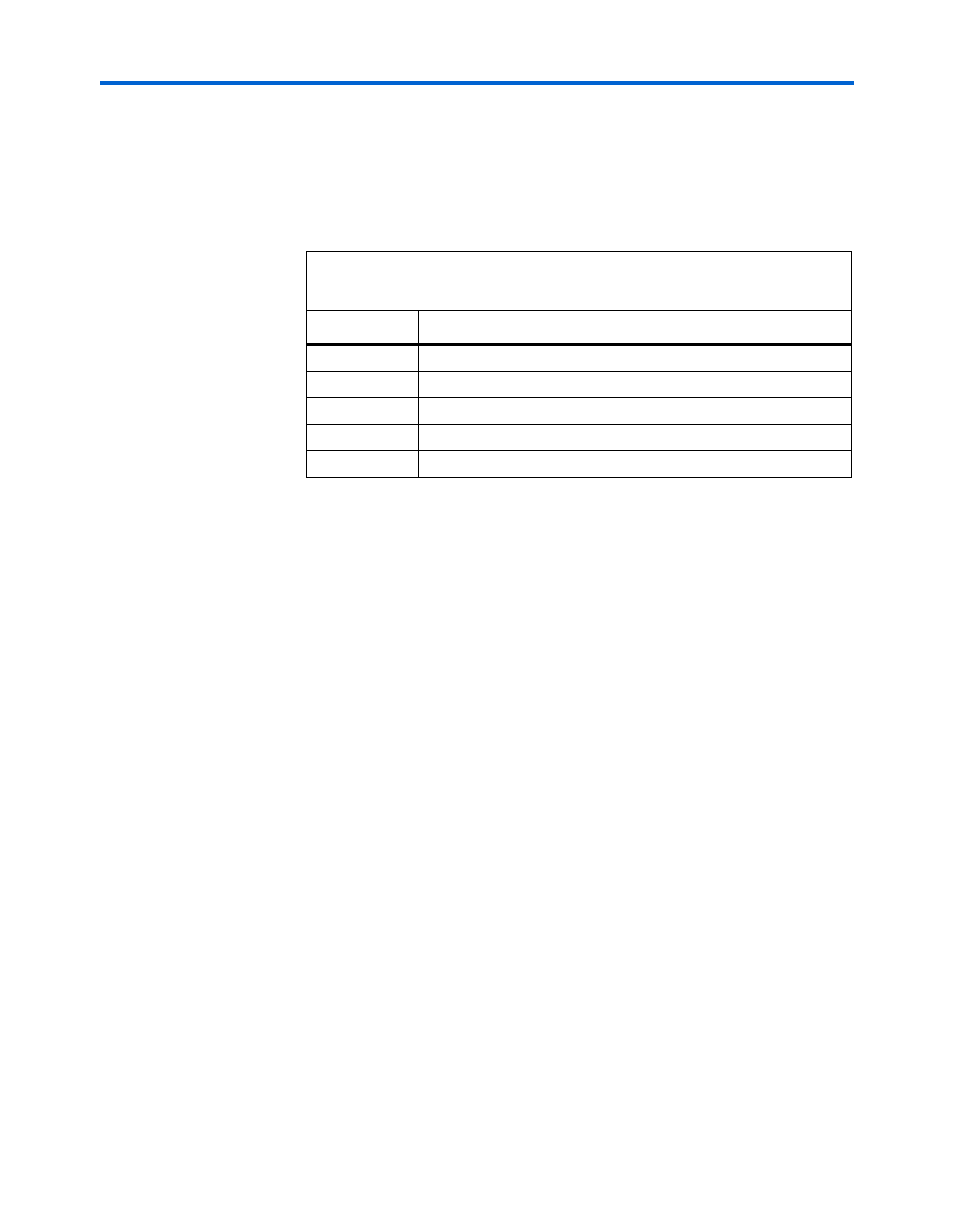

Table 1–2. Device Family and External Memory Support for Quartus II

version 7.2

Device Family

External Memory Supported

Stratix III

DDR2/DDR SDRAM, QDRII+/QDRII SRAM, RLDRAM II

Stratix II

DDR2/DDR SDRAM, QDRII+/QDRII SRAM, RLDRAM II

Stratix II GX

DDR2/DDR SDRAM, QDRII+/QDRII SRAM, RLDRAM II

HardCopy II

DDR2/DDR SDRAM, QDRII+/QDRII SRAM, RLDRAM II

Cyclone II

DDR2/DDR SDRAM

Notes to

:

(1)

DTW support for Stratix III devices is only for design migration from Stratix II

devices. Any new Stratix III designs containing a memory interface must use the

ALTMEMPHY solution. DTW and the dtw_timing_analysis.tcl script do not

support ALTMEMPHY.

(2)

DTW constrains the data path timing for these memory interfaces. The example

driver and the controller are not constrained by the DTW.