Altera DDR Timing Wizard User Manual

Page 14

2–2

Altera Corporation

DDR Timing Wizard User Guide

November 2007

Design Flow

1

You do not need to remove these location assignments

when using DTW even though DTW makes the correct

timing constraints for the paths to these registers.

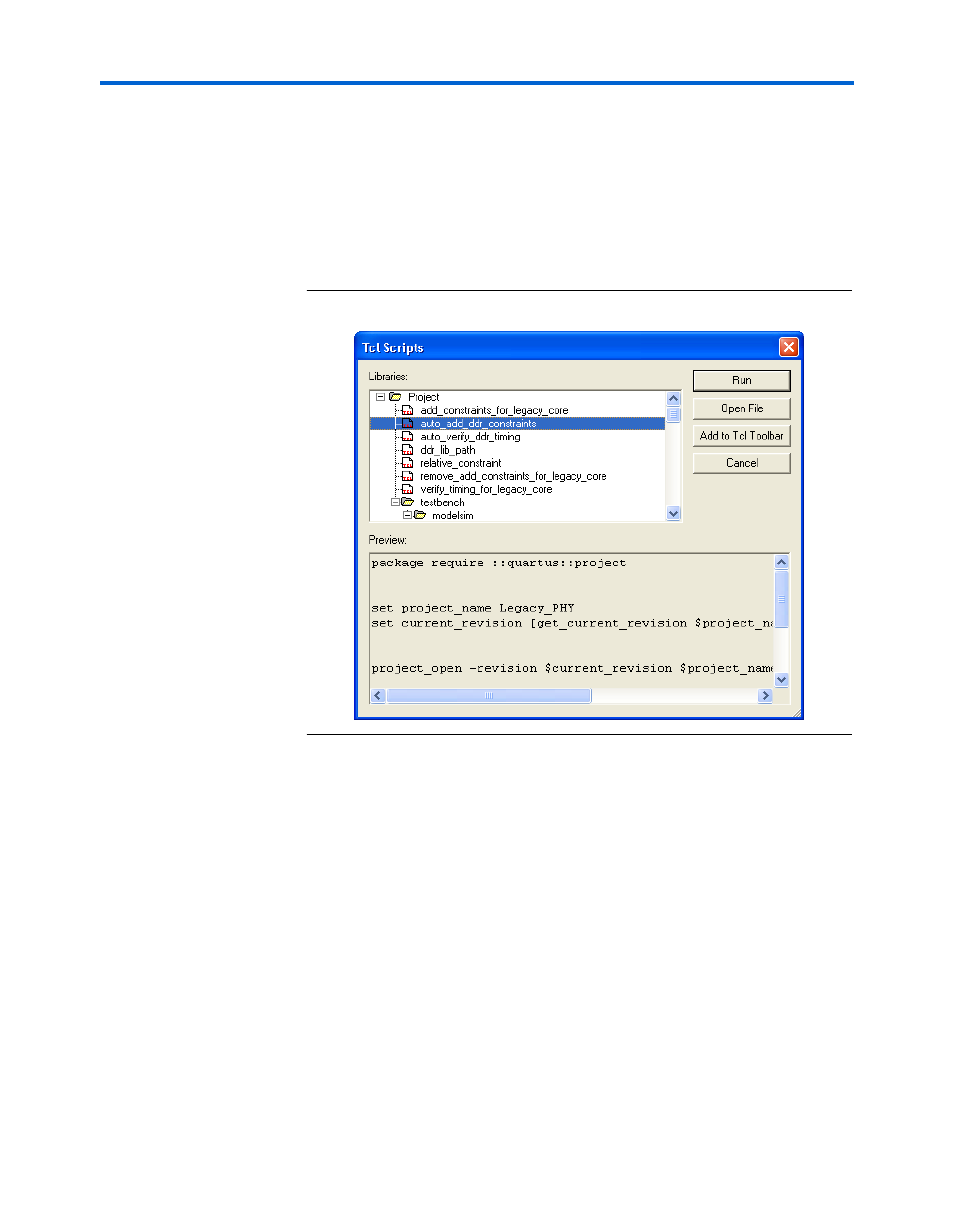

To locate the auto_add_ddr_constraints.tcl script, on the Tools

menu, click Tcl Scripts. The script is under the Project folder.

(

Figure 2–1. Add Constraints TCL Script

After running the auto_add_ddr_constraints.tcl script, assign the

other pin locations, I/O standards, and loading for the design. The

legacy controller MegaWizard does not make pin location

constraints for the command, address, input, and output clock pins.

You can add those constraints using the Quartus II Pin Planner or the

Quartus II Assignment Editor.

1

Place address, command, and clock pins in the same bank

as the DQS/DQ pins to minimize output skew.

3.

Specify timing requirements using DTW.

Because the controller is generated by the legacy controller

MegaWizard, you can import the memory and board specifications

and pin names entered into the legacy controller MegaWizard

instead of manually entering them into the DTW. Also, DTW extracts