Figure 2–21 – Altera DDR Timing Wizard User Manual

Page 41

Altera Corporation

2–29

November 2007

DDR Timing Wizard User Guide

Getting Started

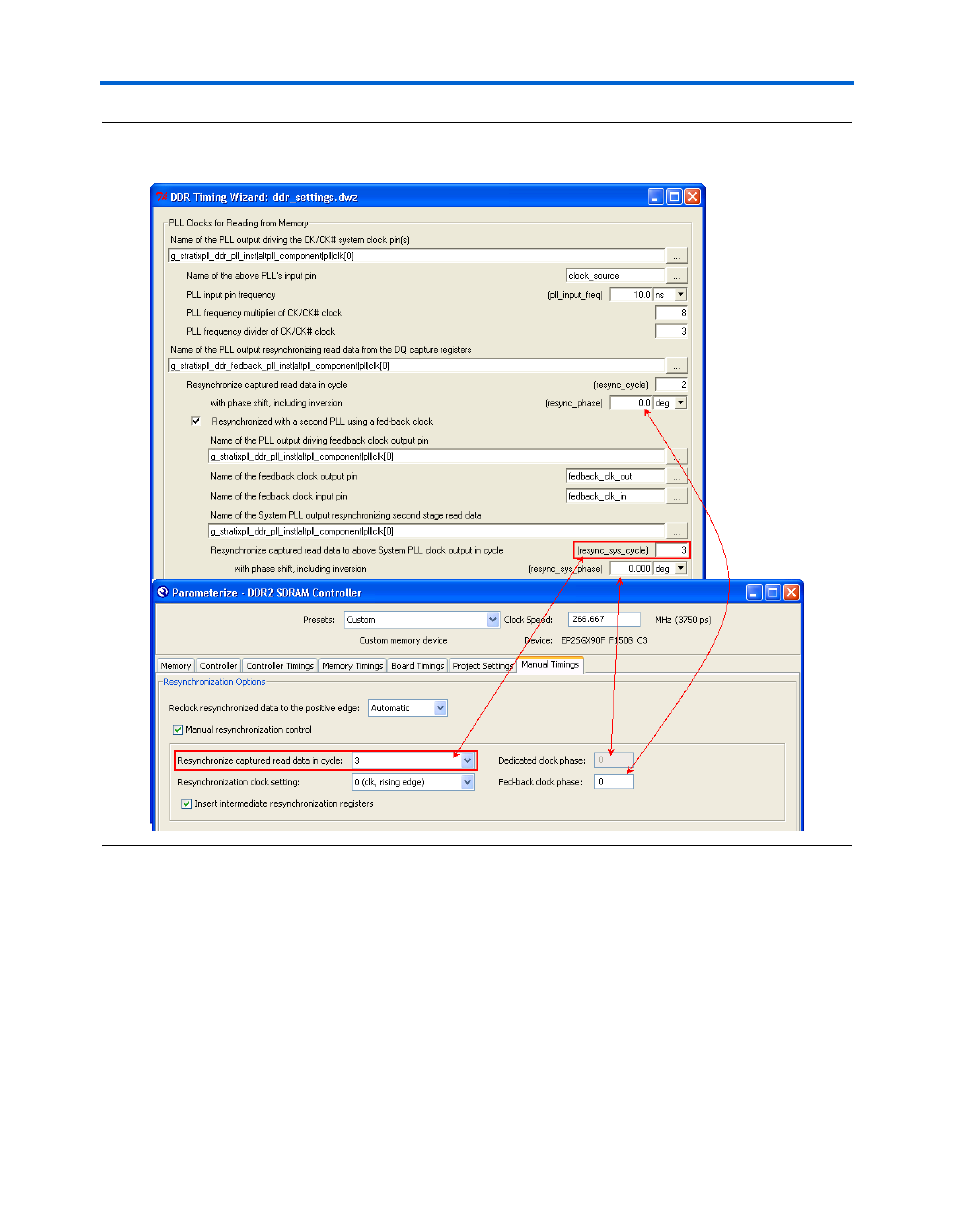

Figure 2–21. Resynchronization Clock and Phase Shift Relationship in DTW and the DDR2/DDR SDRAM

Controller MegaWizard

The Resynchronized with a second PLL using a fed-back clock field

must be checked when using the fedback-clock mode, as the

controlller uses this clock before resynchronizing data back to the

system clock domain. You then must specify the fedback clock input

and output pins, as well as the name of the system PLL output clock

to resynchronize the data from the fedback PLL to the system PLL.

The clock cycle (resync_sys_cycle) and clock phase shift

(resync_sys_phase) in this section should match with the legacy

controller MegaWizard information. If not, you need to fix this

information in DTW. After running the dtw_timing_analysis.tcl