Rx data reception – Altera JESD204B IP User Manual

Page 112

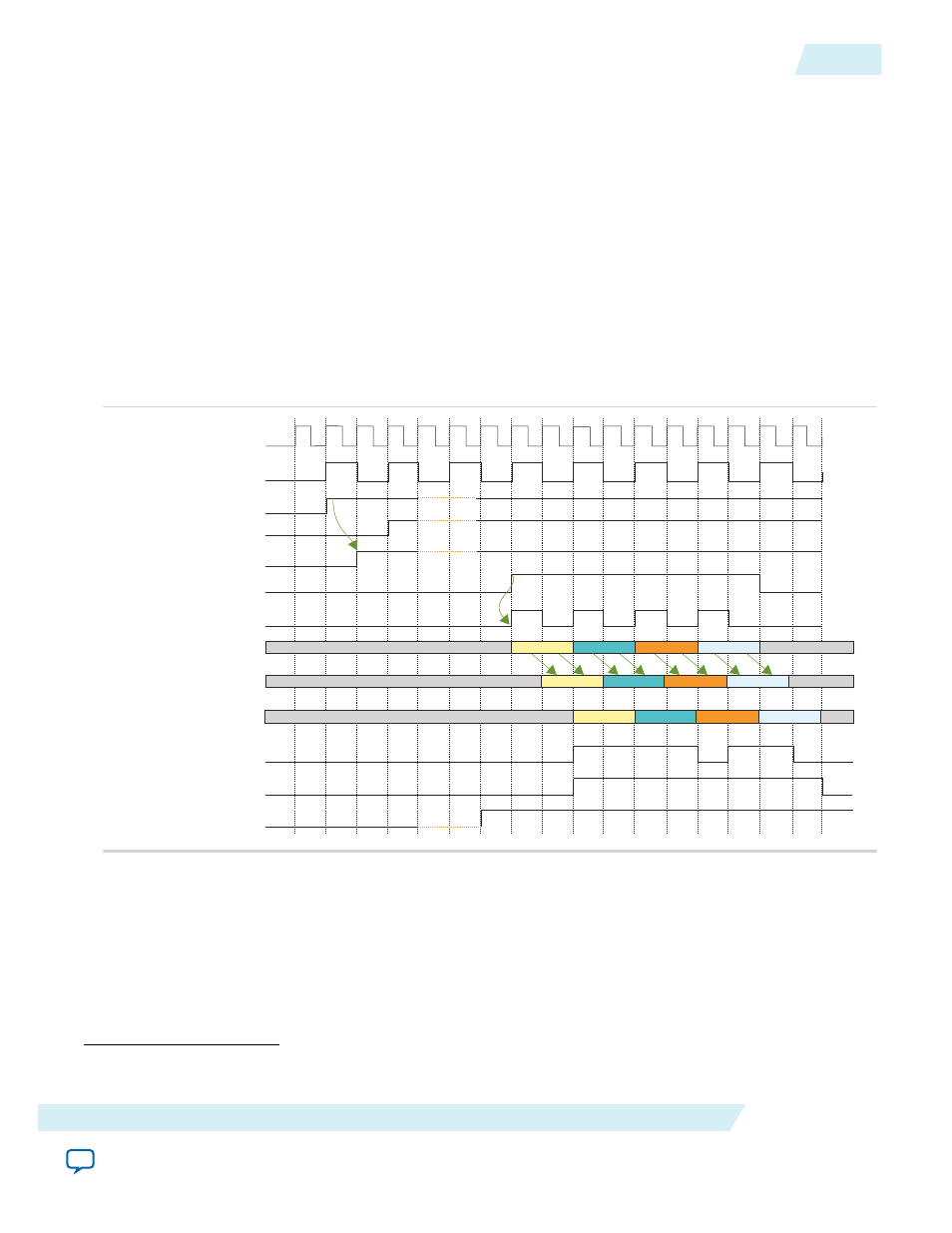

Figure 5-10: RX Operation Behavior

This figure shows the data transmission for a system configuration of LMF = 112, N = 12, N' = 16, S =1.

Operation:

• Upon the deassertion of the

rxframe_rst_n

signal, the

jesd204_rx_link_data_ready

signal from

the deassembler to the DLL is asserted at the next

rxframe_clk

.

• Subsequently, the DLL asserts the

jesd204_rx_link_data_valid

signal for the deassembler to

activate the

f2_div1_cnt

signal logic and to start sampling the

jesd204_rx_link_datain[31:0]

signal.

(36)

• At the following

rxframe_clk

, the

jesd204_rx_data_valid

is asserted along with the multiplexed

jesd204_rx_dataout[11:0]

signal to stream data to the Avalon-ST interface.

• Finally, the DLL deasserts the

jesd204_rx_link_data_valid

signal when there is no more valid data.

• The deassembler deactivates the

f2_div1_cnt

signal logic accordingly, and deasserts the

jesd204_rx_data_valid

at the next

rxframe_clk

.

rxframe_clk

rxlink_clk

rxframe_rst_n

rxlink_rst_n

jesd204_rx_link_data_ready

jesd204_rx_link_data_valid

f2_div1_cnt

jesd204_rx_link_datain[31:0]

rxdata_mux_out[15:0]

jesd204_rx_crtlout[0]

jesd204_rx_data_valid

jesd204_rx_data_ready

junk

xddcc bbaa

junk

junk

junk

xbbaa ddcc x4433 bbaa xddcc 4433

xddc xbba xbba xddc x443 xbba

xddc x443

jesd204_rx_dataout[11:0]

junk

junk

xddc xbba xbba xddc x443 xbba

xddc x443

RX Data Reception

This section explains when there is a valid RX data out from the DLL to the TL to with scrambler enabled.

The MAC layer process the

jesd204_rx_dataout

signal once the TL asserts the

jesd204_rx_data_valid

signal. However, there are some data that should be discarded by the upper layer when the you enable the

scrambler. This is because the initial unknown seed value within the scrambler can corrupt the very first

eight octets, which is the data for the first two link clock cycles. The data can be translated to the frame

(36)

The

f2_div1_cnt

signal is internally generated in the RX control block to correctly stream data to the

Avalon-ST interface.

UG-01142

2015.05.04

RX Data Reception

5-31

JESD204B IP Core Design Guidelines

Altera Corporation