Pll reconfiguration, Transceiver reconfiguration controller – Altera JESD204B IP User Manual

Page 85

Related Information

•

on page 4-18

More information about the JESD204B IP core clocks.

PLL Reconfiguration

The PLL reconfiguration utilizes the ALTERA_PLL_RECONFIG IP core to implement reconfiguration

logic to facilitate dynamic real-time reconfiguration of PLLs in Altera devices. You can use this megafunc‐

tion IP core to update the output clock frequency, PLL bandwidth, and phase shifts in real time, without

reconfiguring the entire FPGA.

The design example uses the MIF approach to reconfigure the core PLL. The ALTERA_PLL_RECONFIG

IP core has two parameter options—Enable MIF Streaming and Path to MIF file—for the MIF input.

Turn on Enable MIF Streaming option and set the core_pll.mif as the value to Path to MIF file

parameter.

The following PLL reconfiguration Avalon-MM operations occurs during data rate reconfiguration.

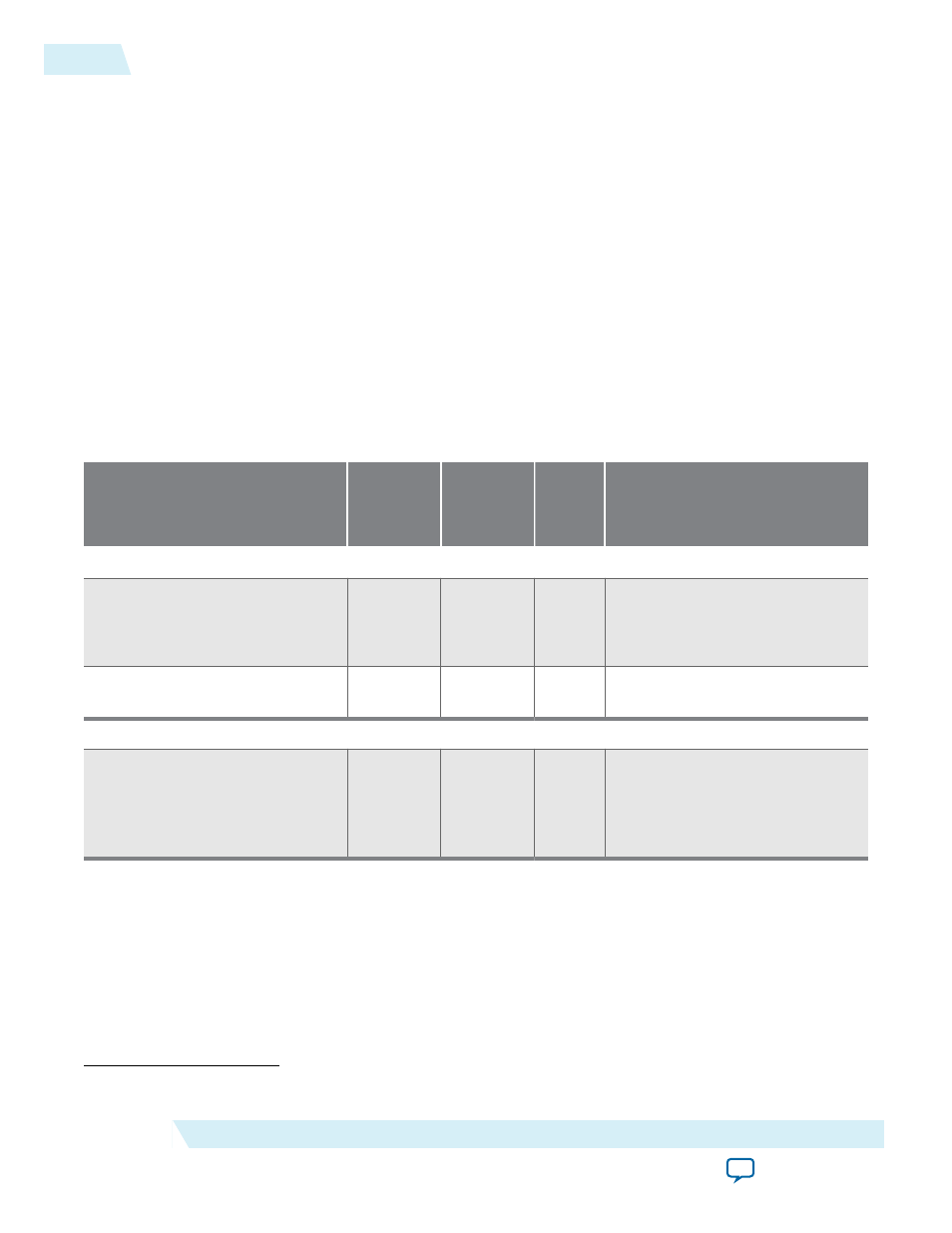

Table 5-1: PLL Reconfiguration Operation

Operation

Avalon-MM

Interface

Signal

Byte

Address

Offset

(6bits)

Bit

Value

Arria V and Stratix V Devices

Set MIF base address

pll_mgmt_* 0x01F

[8:0]

0x000 (maximum configuration)

or

0x02E (downscale configuration)

Write to the START register to

begin

pll_mgmt_* 0x02

[0:0]

0x01

Arria 10 Devices

Start MIF streaming with MIF

base address specified in data

value

pll_mgmt_* 0x010

[31:0]

0x000 (maximum configuration)

or

0x02E (downscale configuration)

(28)

Related Information

More information about the MIF streaming option.

Transceiver Reconfiguration Controller

The transceiver reconfiguration controller allows you to change the device transceiver settings at any

time. Any portion of the transceiver can be selectively reconfigured. Each portion of the reconfiguration

(28)

The MIF base address is 9 bits (LSB). The remaining bits are reserved.

5-4

PLL Reconfiguration

UG-01142

2015.05.04

Altera Corporation

JESD204B IP Core Design Guidelines