Altera JESD204B IP User Manual

Page 14

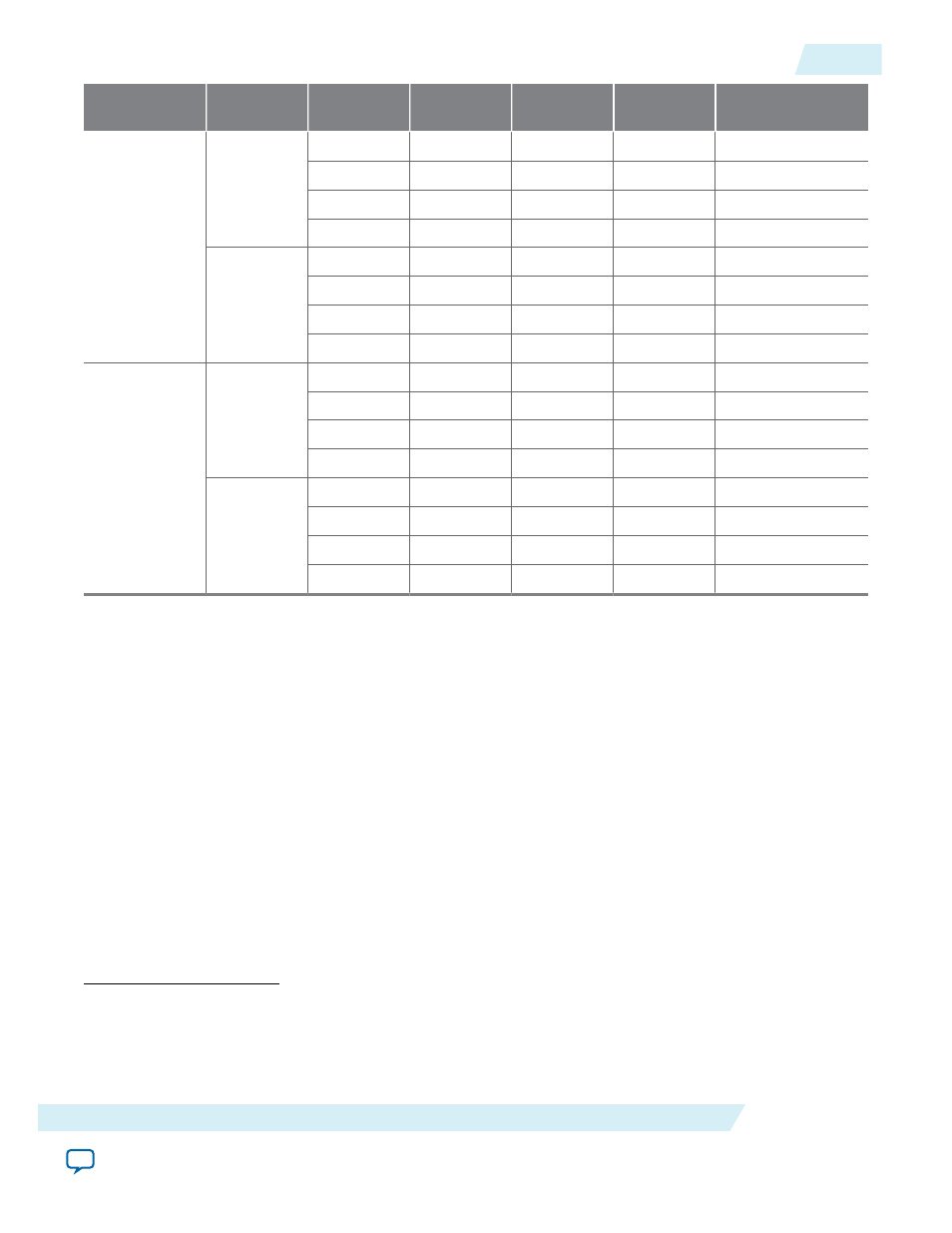

Device Family

Data Path

Number of

Lanes

ALMs

ALUTs

Logic

Registers

Memory Block

(M10K/M20K)

(6)

(7)

Arria 10

RX

1

1043

1504

1194

0

2

1575

2265

1815

0

4

2828

3927

3060

0

8

5356

7347

5546

0

TX

1

695

1092

931

0

2

878

1373

1049

0

4

1240

1888

1285

0

8

1908

2969

1757

0

Stratix V

RX

1

1056

1542

1215

0

2

1642

2363

1857

0

4

2936

4097

3140

0

8

5546

7697

5712

0

TX

1

719

1150

948

0

2

937

1488

1083

0

4

1358

2114

1353

0

8

2137

3417

1894

0

Related Information

•

•

Information about the Quartus II resource utilization reporting, including ALMs needed.

(6)

M10K for Arria V device, M20K for Arria V GZ, Stratix V and Arria 10 devices.

(7)

The Quartus II software may auto-fit to use MLAB when the memory size is too small. Conversion from

MLAB to M20K or M10K was performed for the numbers listed above.

(7)

The Quartus II software may auto-fit to use MLAB when the memory size is too small. Conversion from

MLAB to M20K or M10K was performed for the numbers listed above.

UG-01142

2015.05.04

Performance and Resource Utilization

2-9

About the JESD204B IP Core

Altera Corporation