Reset scheme, Reset scheme -24 – Altera JESD204B IP User Manual

Page 61

Related Information

•

•

•

on page 4-22

Reset Scheme

All resets in the JESD204B IP core are synchronous reset signals and should be asserted and deasserted

synchronously.

Note: Ensure that the resets are synchronized to the respective clocks for reset assertion and deassertion.

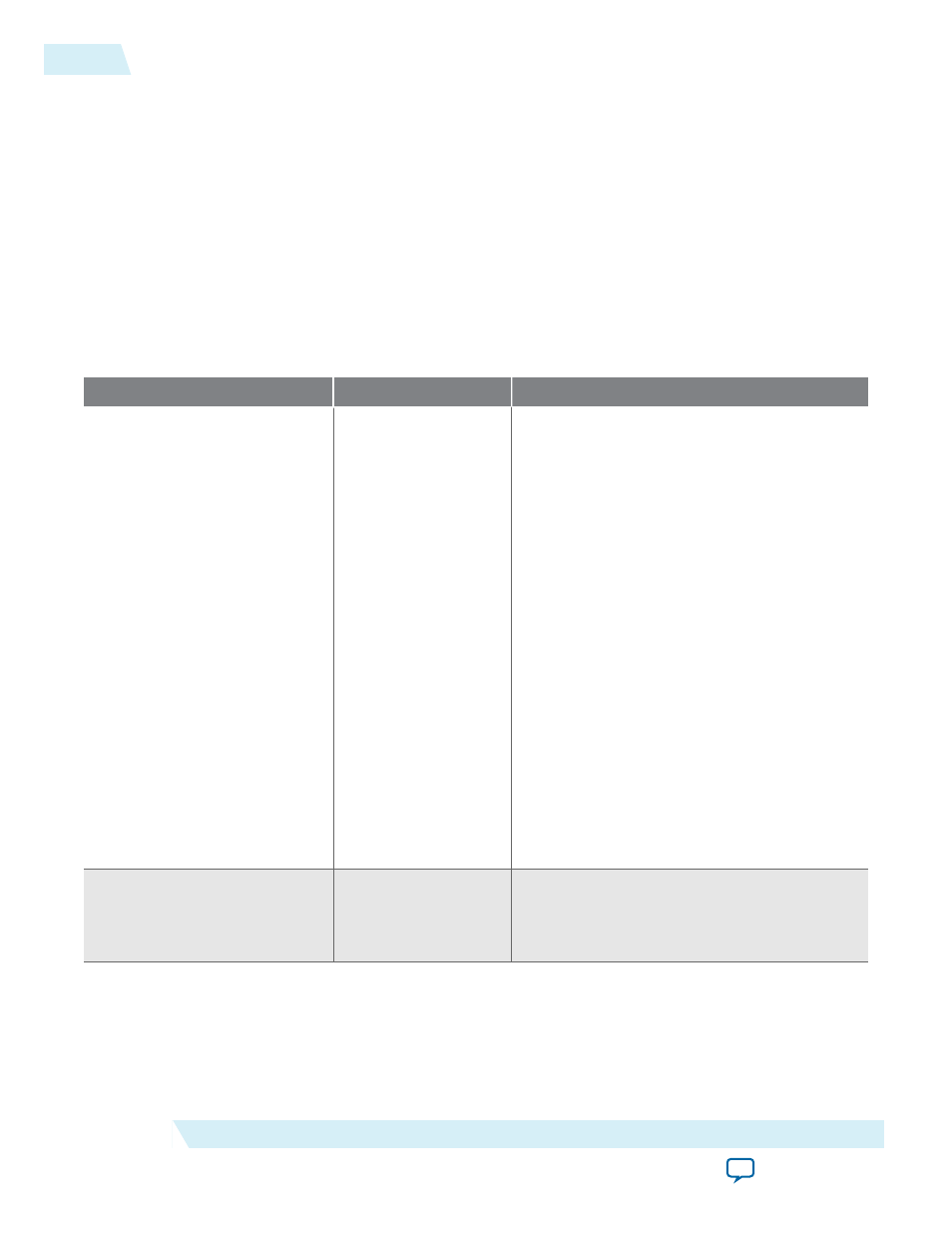

Table 4-4: JESD204B IP Core Resets

Reset Signal

Associated Clock

Description

txlink_rst_n

rxlink_rst_n

TX/RX Link Clock

Active low reset controlled by the clock and

reset unit.

Altera recommends that you:

• Assert the

txlink_rst_n

/

rxlink_rst_n

and

txframe_rst_n

/

rxframe_rst_n

signals when the transceiver is in reset.

• Deassert the

txlink_rst_n

and

txframe_

rst_n

signals after the Altera PLL IP core is

locked and the

tx_ready[]

signal from the

Transceiver Reset Controller is asserted.

• Deassert the

rxlink_rst_n

and

rxframe_

rst_n

signals after the Transceiver CDR

rx_islockedtodata[]

signal and

rx_

ready[]

signal from the Transceiver Reset

Controller are asserted.

The

txlink_rst_n

/

rxlink_rst_n

and

txframe_rst_n

/

rxframe_rst_n

signals can

be deasserted at the same time. These resets

can only be deasserted after you configure the

CSR registers.

txframe_rst_n

rxframe_rst_n

TX/RX Frame Clock

Active low reset controlled by the clock and

reset unit. If the TX/RX link clock and the TX/

RX frame clock has the same frequency, both

can share the same reset.

4-24

Reset Scheme

UG-01142

2015.05.04

Altera Corporation

JESD204B IP Core Functional Description