Control unit – Altera JESD204B IP User Manual

Page 118

example. The subsequent 13 bits represent the starting address of the data sent. The last 8 bits are register

data.

For a 32-bit SPI transaction, each SPI programming cycle needs to be preceded with a preselection byte.

The preselection byte is typically used to forward the SPI command to the right destination.

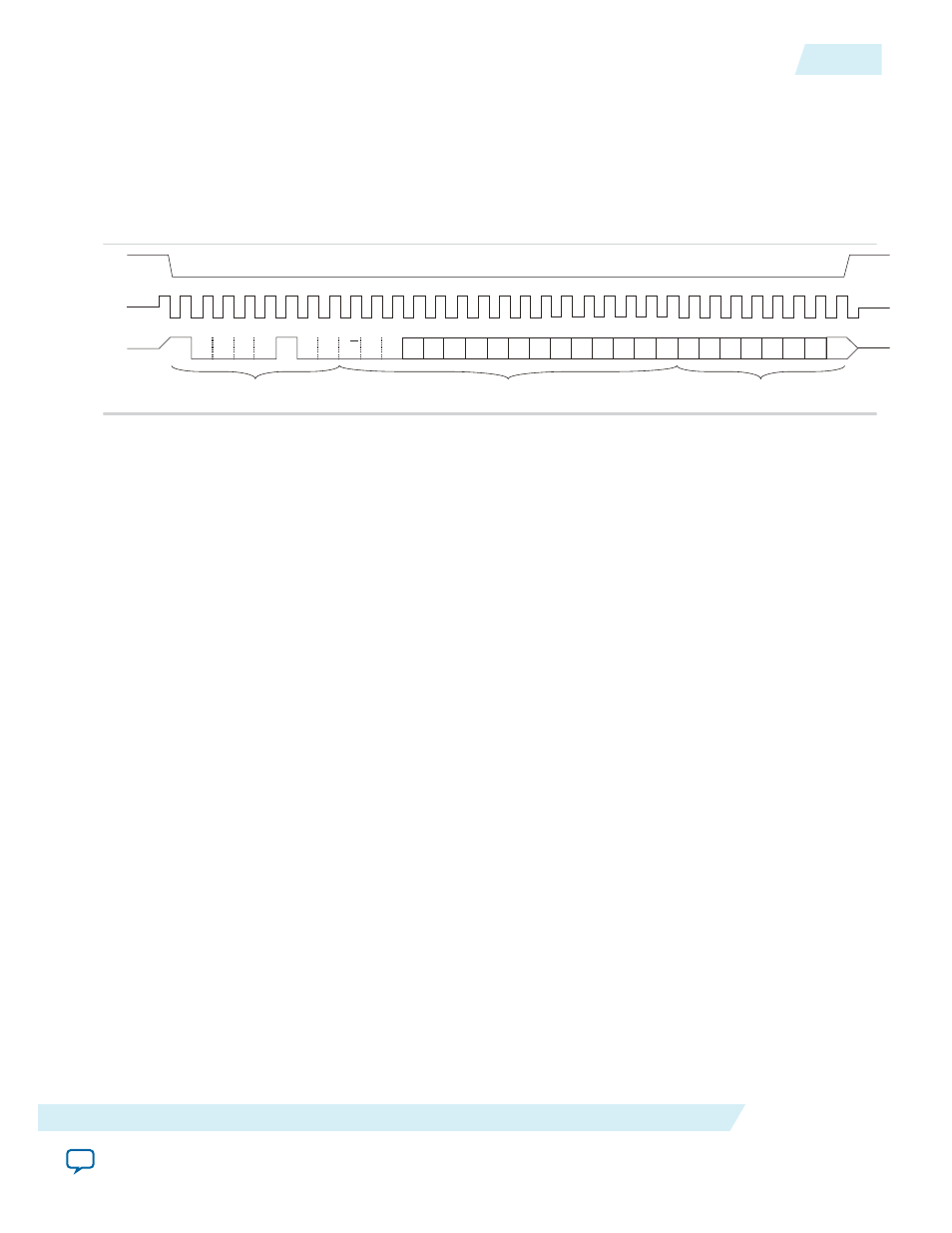

figure

shows

the timing diagram of a 32-bit SPI transaction.

Figure 5-14: Serial Port Interface (32-bit) Timing Diagram

A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0

P7 P6 P5 P4 P3 P2 P1 P0 R/W W1 W0

8 Bit Pre-Selection

8 Bit Register Data

16 Bit Instruction

SS_n

SCLK

SDIO

In this design example, the SPI core is configured as a 4-wire master protocol to control three

independent SPI slaves—ADC, DAC, and clock devices. The width of the receive and transmit registers

are configured at 32 bits. Data is sent in MSB-first mode in compliance with the converter device default

power up mode. The SPI clock (

sclk

) rate is configured at a frequency of the SPI input clock rate divided

by 5. If the SPI input clock rate is 100 MHz (in the

mgmt_clock

domain), the

sclk

rate is 20 MHz. If the

external converter device's SPI interface is a 3-wire protocol without both MOSI (master output, slave

input) and MISO (master input, slave output) lines but with a single DATAIO pin, you can use the

ALTIOBUF Megafunction IP core (configured with bidirectional buffer) with the SPI master to convert

the MOSI and MISO lines to a single DATAIO pin. The DATAIO pin can be dynamically reconfigured as

MOSI by asserting the output enable (

oe

) signal or as MISO by deasserting the

oe

signal. For implementa‐

tion simplicity, you can directly connect the master MOSI pin to the slave DATAIO pin if read transac‐

tions are not required.

Related Information

More information about configuring the ALTIOBUF Megafunction IP Core.

Control Unit

The control unit has access to the CSR interface of the JESD204B IP core duplex base core, PLL

reconfiguration, transceiver reconfiguration controller, and SPI master. The control unit also serves as a

clock and reset unit (CRU) for the design example.

The control unit replaces the software-based Nios II processor to perform device configuration and

initialization on the JESD204B duplex base core. This configuration and initialization process includes the

transceivers, transport layer, pattern generator and checker, external converters (ADC/DAC), and clock

devices over the SPI interface.

UG-01142

2015.05.04

Control Unit

5-37

JESD204B IP Core Design Guidelines

Altera Corporation