Altera JESD204B IP User Manual

Page 78

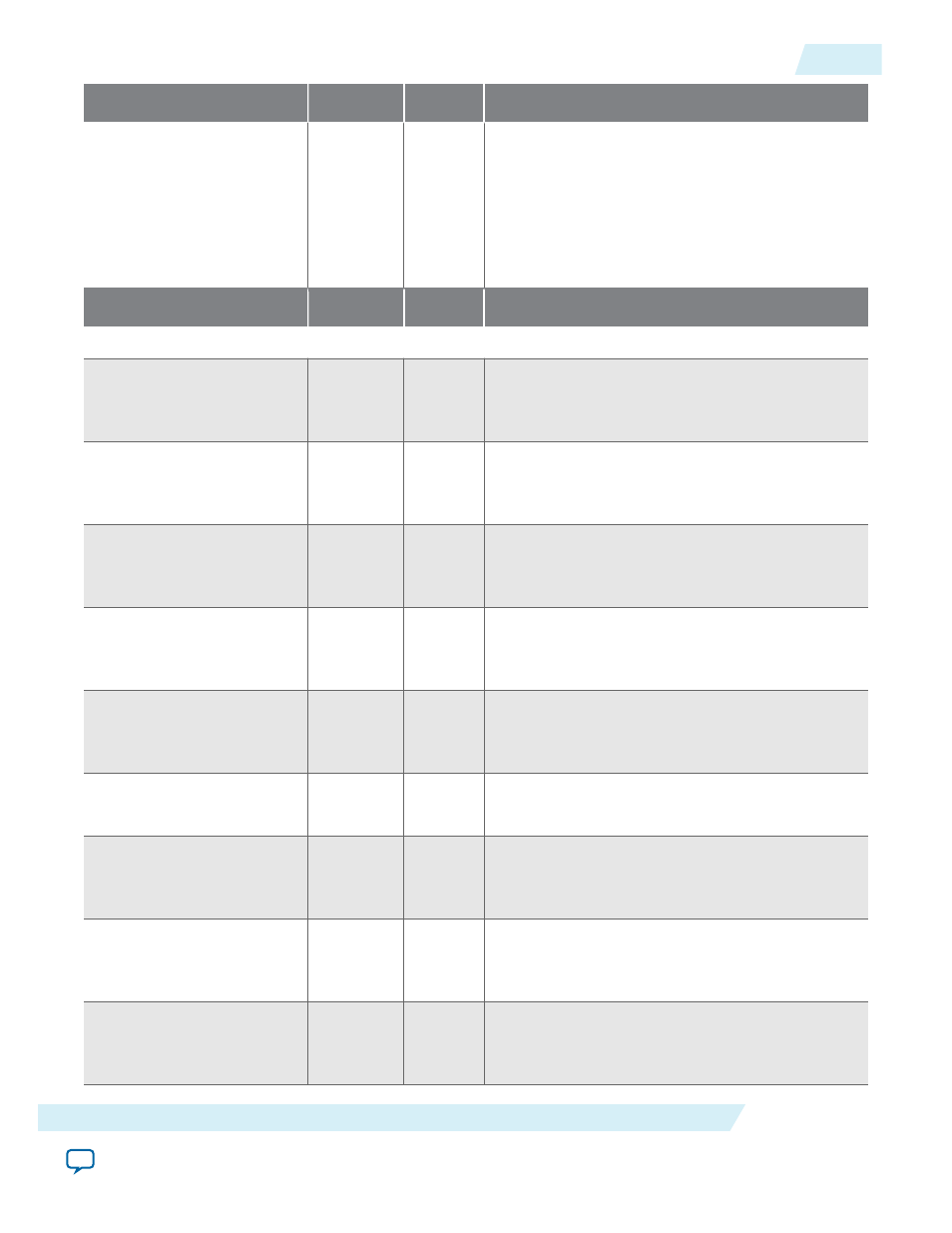

Signal

Width

Direction

Description

alldev_lane_aligned

1

Input

Aligns all lanes for this device.

For multidevice synchronization, multiplex all the

dev_lane_aligned

signals before connecting to

this signal pin.

For single device support, connect the

dev_lane_

aligned

signal back to this signal.

Signal

Width

Direction

Description

CSR

csr_l[]

5

Output

Indicates the number of active lanes for the link.

The transport layer can use this signal as a run-

time parameter.

csr_f[]

8

Output

Indicates the number of octets per frame. The

transport layer can use this signal as a run-time

parameter.

csr_k[]

5

Output

Indicates the number of frames per multiframe.

The transport layer can use this signal as a run-

time parameter.

csr_m[]

8

Output

Indicates the number of converters for the link.

The transport layer can use this signal as a run-

time parameter.

csr_cs[]

2

Output

Indicates the number of control bits per sample.

The transport layer can use this signal as a run-

time parameter.

csr_n[]

5

Output

Indicates the converter resolution. The transport

layer can use this signal as a run-time parameter.

csr_np[]

5

Output

Indicates the total number of bits per sample. The

transport layer can use this signal as a run-time

parameter.

csr_s[]

5

Output

Indicates the number of samples per converter per

frame cycle. The transport layer can use this signal

as a run-time parameter.

csr_hd

1

Output

Indicates the high density data format. The

transport layer can use this signal as a run-time

parameter.

UG-01142

2015.05.04

Receiver

4-41

JESD204B IP Core Functional Description

Altera Corporation