Altera JESD204B IP User Manual

Page 68

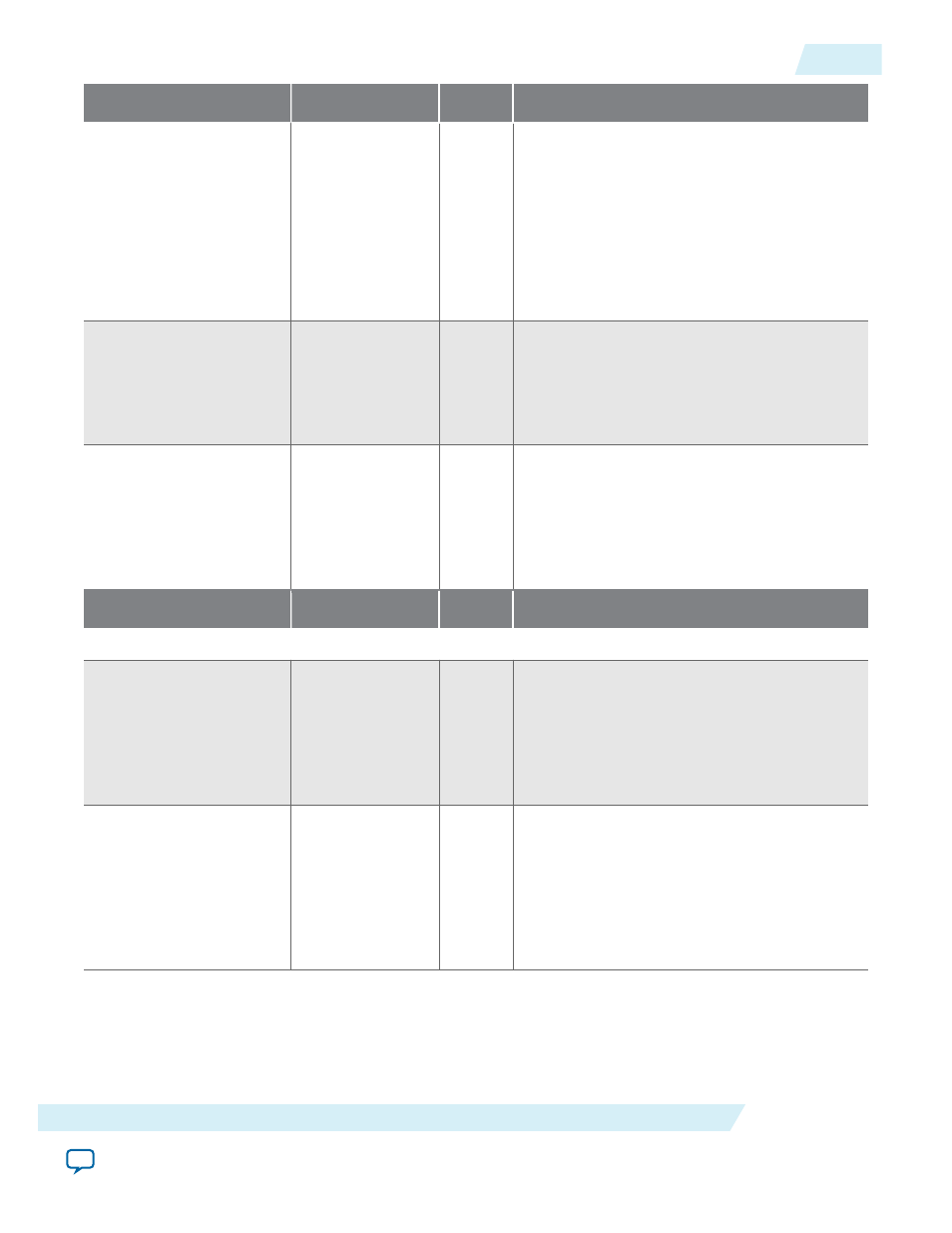

Signal

Width

Direction

Description

jesd204_tx_link_

valid

1

Input

Indicates whether the data from the transport

layer is valid or invalid. The Avalon-ST sink

interface in the TX core cannot be backpres‐

sured and assumes that data is always valid on

every cycle when the

jesd204_tx_link_ready

signal is asserted.

• 0—data is invalid

• 1—data is valid

jesd204_tx_link_

ready

1

Output

Indicates that the Avalon-ST sink interface in

the TX core is ready to accept data. The

Avalon-ST sink interface asserts this signal on

the JESD204B link state of USER_DATA

phase. The ready latency is 0.

jesd204_tx_frame_

ready

1

Output

Indicates that the Avalon-ST sink interface in

the transport layer is ready to accept data. The

Avalon-ST sink interface asserts this signal on

the JESD204B link state of ILAS 4

th

multiframe and also the USER_DATA phase.

The ready latency is 0.

Signal

Width

Direction

Description

Avalon-MM Interface

jesd204_tx_avs_clk

1

Input

The Avalon-MM interface clock signal. This

clock is asynchronous to all the functional

clocks in the JESD204B IP core. The

JESD204B IP core can handle any cross clock

ratio and therefore the clock frequency can

range from 75 MHz to 125 MHz.

jesd204_tx_avs_rst_n

1

Input

This reset is associated with the

jesd204_tx_

avs_clk

signal. This reset is an active low

signal. You can assert this reset signal

asynchronously but must deassert it synchro‐

nously to the

jesd204_tx_avs_clk

signal.

After you deassert this signal, the CPU can

configure the CSRs.

UG-01142

2015.05.04

Transmitter

4-31

JESD204B IP Core Functional Description

Altera Corporation