Altera JESD204B IP User Manual

Page 156

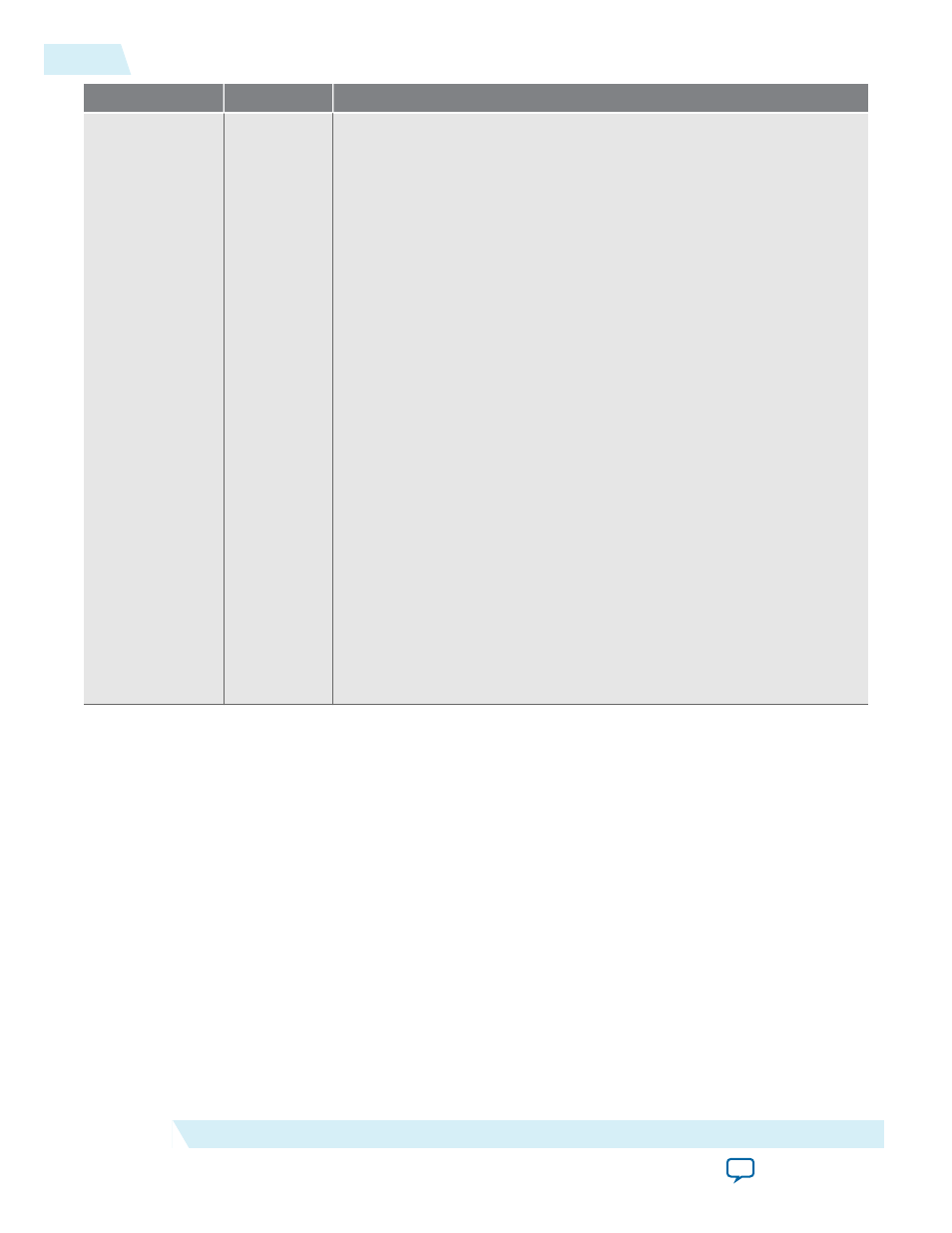

Date

Version

Changes

December

2014

2014.12.15 • Updated the JESD204B IP Core FPGA Performance table with the

data rate range.

• Updated the JESD204B IP Core FPGA Resource Utilization table.

• Updated the JESD204B IP Core Parameters table with the following

changes:

• Revised the parameter name of Enable PLL/CDR Dynamic

Reconfiguration to Enable Transceiver Dynamic Reconfigura‐

tion.

• Added information for a new parameter—Enable Altera Debug

Master Endpoint.

• Added details about the rule check for parameter N' value.

Integrating the JESD204B IP core in Qsys

on

page 3-11.

• Updated

,

• Added a new table—Register Access Type Convention—to describe

the access type for the IP core registers.

• Added new signals description for

jesd204_tx_controlout

and

jesd204_rx_controlout

.

• Added CONTROL_BUS_WIDTH parameter and description for the

assembler and deassembler.

• Added information on how to run the Tcl script using the Quartus II

sofware before compiling the design example.

• Updated the section on

Debugging JESD204B Link Using SignalTap

on page 7-3 with verification information for

TX PHY-link layer interface, TX link layer, and TX transport layer

operations.

8-2

JESD204B IP Core Document Revision History

UG-01142

2015.05.04

Altera Corporation

Additional Information