Finite state machine (fsm) – Altera JESD204B IP User Manual

Page 120

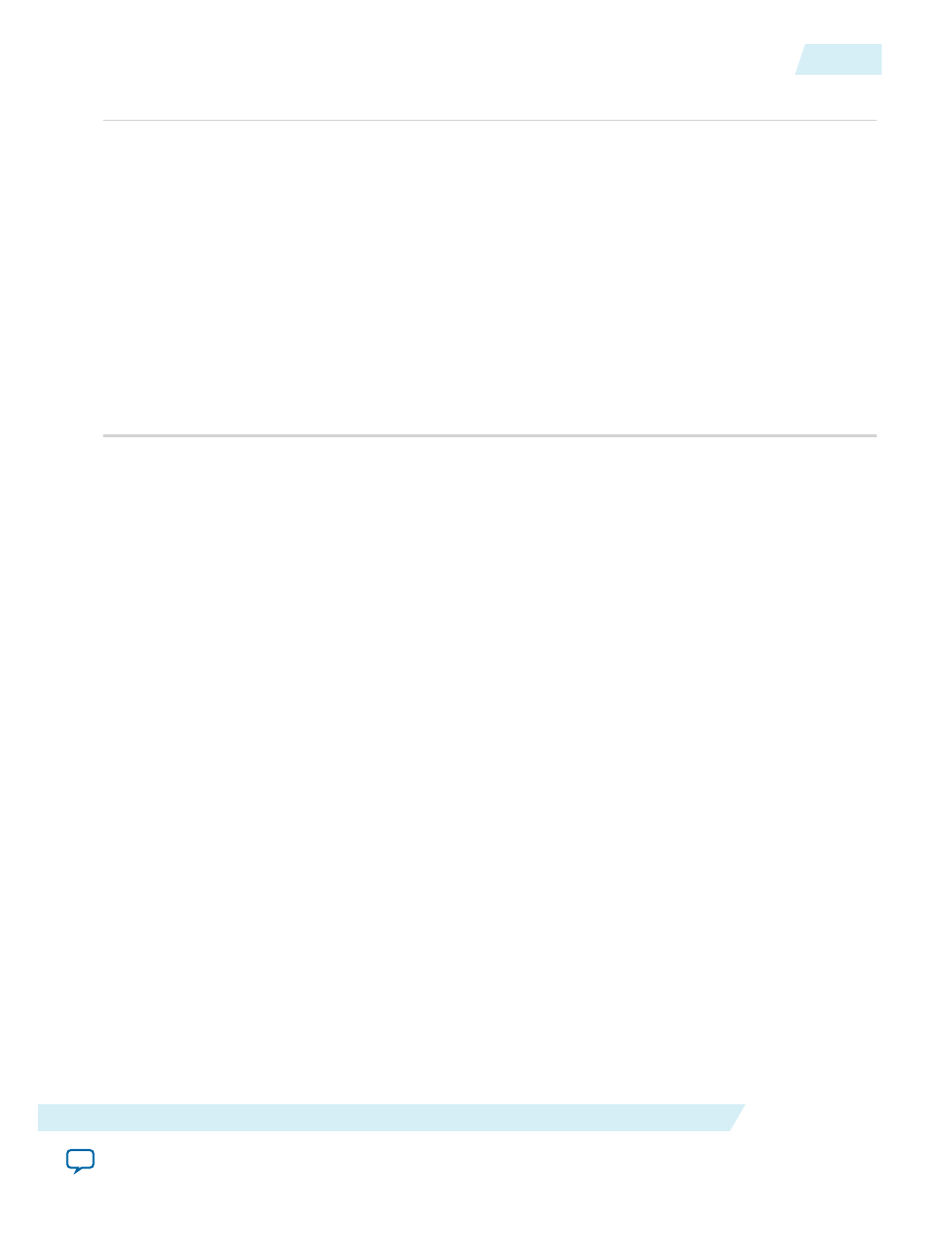

Figure 5-16: Example of MIF Format and Content

-- MIF content for ADC

WIDTH=24; -- the size of data in bits

DEPTH=8; -- the size of memory in words

ADDRESS_RADIX=UNS; -- the radix for address values

DATA_RADIX=BIN; -- the radix for data values

CONTENT BEGIN

0 : 000000000101111100010101; -- write 0x15 to link control 1 register 0x5F to disable the lane

1 : 000000000101111001000100; -- write 0x44 to quick config register 0x5E for L=4, M=4

2 : 000000000110010011000000; -- write 0xC0 to DID register 0x64

3 : 000000000110111000000011; -- write 0x03 to parameter SCR/L register 0x6E to disable scrambler

4 : 000000000111000000001111; -- write 0x0F to parameter K register 0x70 for K=16 in base IP core

5 : 000000000000110100000100; -- write 0x04 to test mode register 0x0D for checkerboard test pattern

6 : 000000000101111100010100; -- write 0x14 to link control 1 register 0x5F to enable the lane

7 : 111111111111111111111111; -- indicates end of mif or end of programming sequence

END;

The initial values for each address and sequence is defined based on the requirement of the external

converter and clock devices. The example above is based on 24-bit SPI write-only programming.

The last word must not be a valid data and must be set to all 1's to indicate the end of the MIF or

programming sequence. This is because each converter device may have a different number of

programmable registers and hence involves a different number of MIF words. In this design example,

three ROMs are used by default for each external ADC, DAC, and clock devices. If either one of the device

is not used, a single word MIF with all 1's can be created.

Note: The MIFs in this design example is an example for a particular converter device. You must define

the MIF content based on the requirement of the external converter devices.

Finite State Machine (FSM)

The steps below describe the FSM flow:

1. Initialize the SPI:

a. Perform a read transaction from the ROM on per word basis and write to the SPI master for SPI

write transaction to the external SPI slave.

b. Perform a read transaction from the next ROM and perform the same SPI write transaction to next

SPI slave.

2. Initialize the JESD204B IP base core, transport layer, pattern generator, and pattern checker upon

successful initialization of the transceiver.

UG-01142

2015.05.04

Finite State Machine (FSM)

5-39

JESD204B IP Core Design Guidelines

Altera Corporation