Tx path operation – Altera JESD204B IP User Manual

Page 97

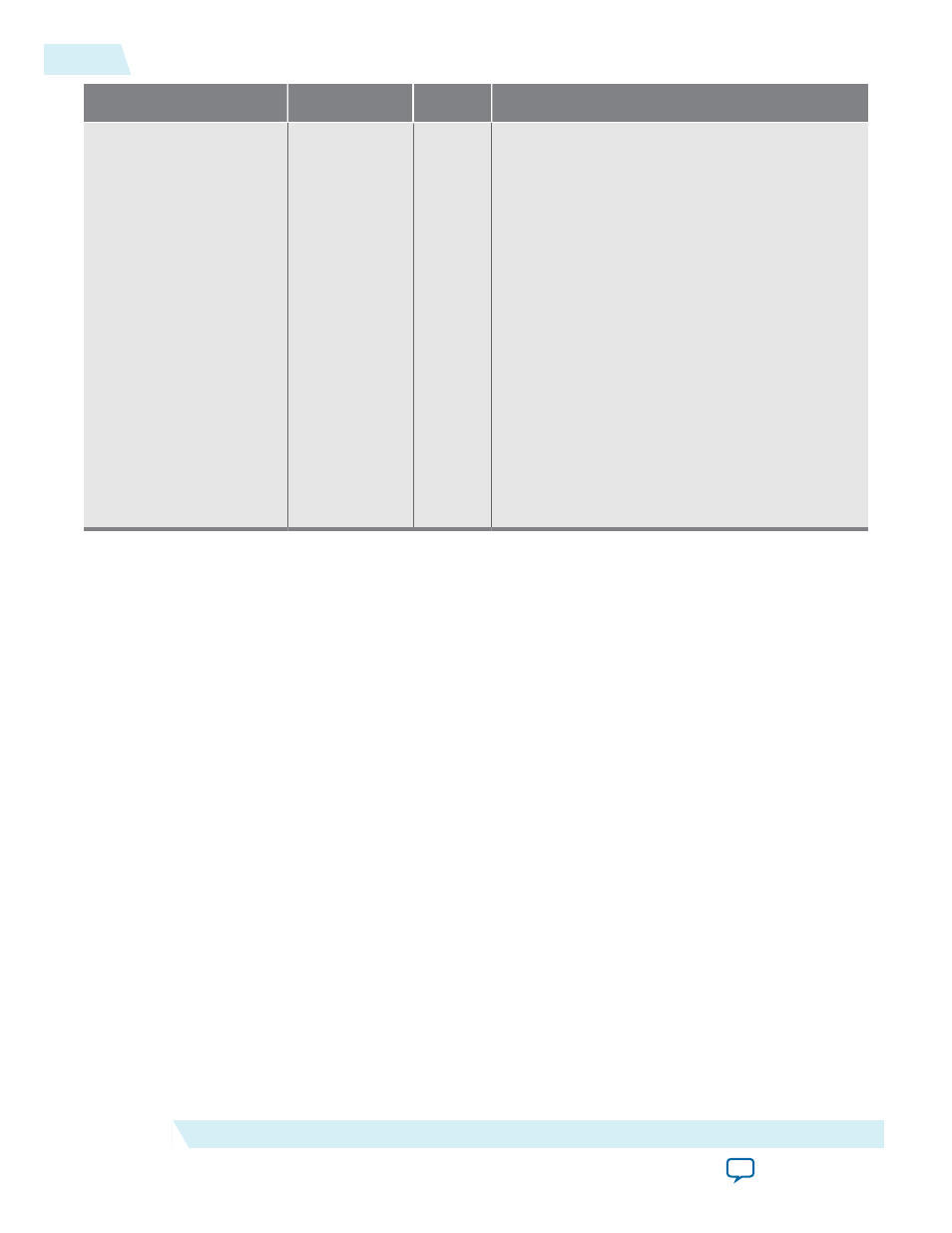

Signal

Clock Domain

Direction

Description

csr_n[4:0]

(31)

mgmt_clk

Input

Indicates the converter resolution. This 5-bit bus

represents the N value in zero-based binary

format. For example, if N = 16, the

csr_n[4:0]

=

"01111". This design example supports the

following values:

• 01011

• 01100

• 01101

• 01110

• 01111

Any programmed value beyond the supported

range may result in undeterminable behavior in

the transport layer. You must ensure that the

csr_n[4:0]

value always match the system

parameter N value.

Connect this signal to the TX DLL

csr_n[]

output pin.

TX Path Operation

The data transfer protocol between the Avalon-ST interface and the TX path transport layer is data

transfer with backpressure, where ready_latency = 0.

5-16

TX Path Operation

UG-01142

2015.05.04

Altera Corporation

JESD204B IP Core Design Guidelines