BECKHOFF EtherCAT IP Core for Altera FPGAs v3.0.10 User Manual

Page 130

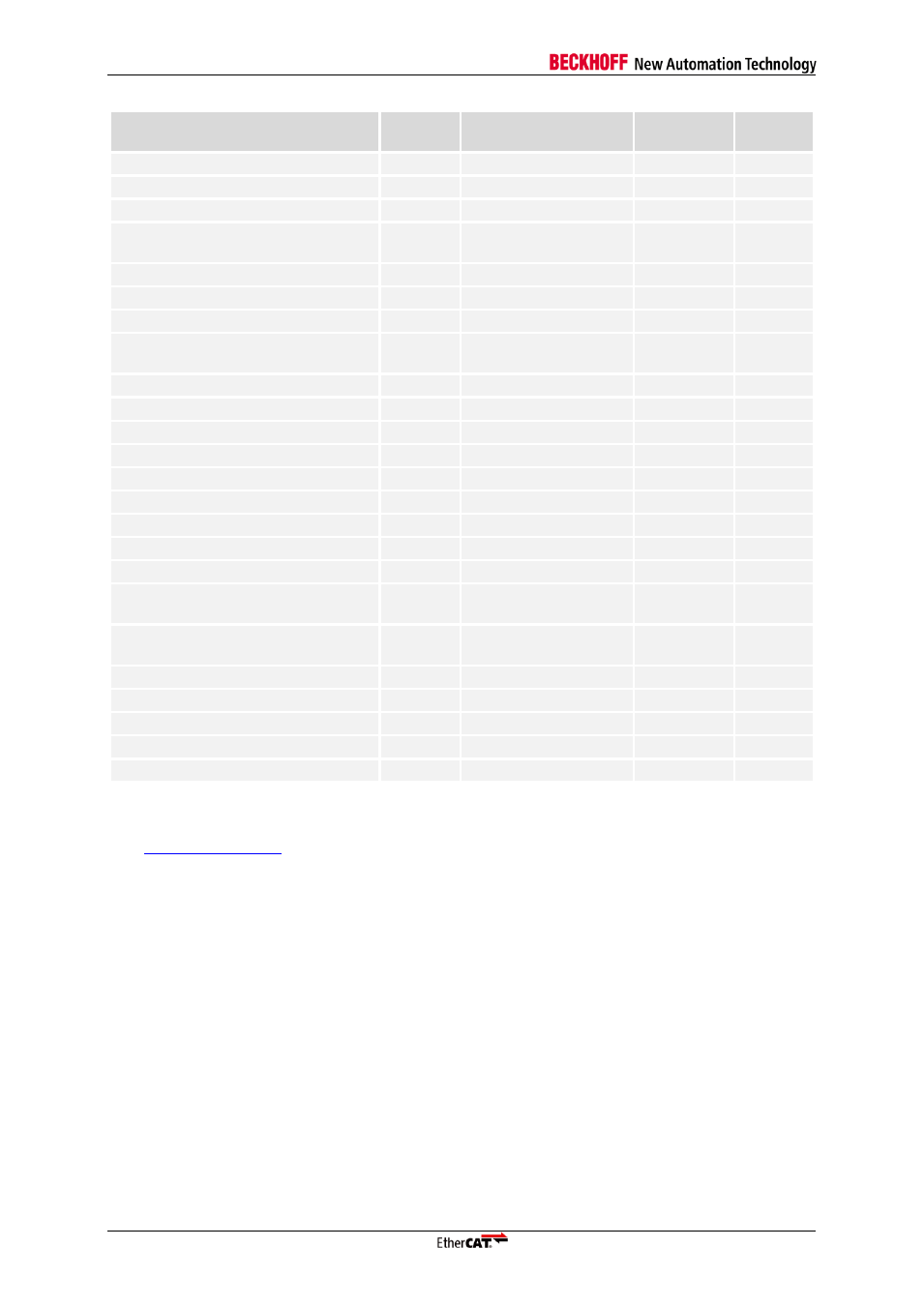

PDI Description

III-118

Slave Controller

– IP Core for Altera FPGAs

Signal

Directio

n

Description

Channel

Signal

polarity

PDI_AXI_WLAST

IN

Write data last

WR data

act. high

PDI_AXI_WVALID

IN

Write data valid

WR data

act. high

PDI_AXI_WREADY

OUT

Write data ready

WR data

act. high

PDI_AXI_BID

[PDI_BUS_ID_WIDTH-1:0]

OUT

Write response ID

WR resp.

PDI_AXI_BRESP[1:0]

OUT

Write response

WR resp.

PDI_AXI_BVALID

OUT

Write response valid

WR resp.

act. high

PDI_AXI_BREADY

IN

Write response ready

WR resp.

act. high

PDI_AXI_ARID

[PDI_BUS_ID_WIDTH-1:0]

IN

Read address ID

RD addr.

PDI_AXI_ARADDR[15:0]

IN

Read address

RD addr.

PDI_AXI3_ARLEN[3:0]

IN

Read length

RD addr.

PDI_AXI_ARSIZE[2:0]

IN

Read size

RD addr.

PDI_AXI_ARBURST[1:0]

IN

Read burst type

RD addr.

PDI_AXI3_ARLOCK

IN

Read lock

RD addr.

PDI_AXI_ARCACHE[3:0]

IN

Read cache type

RD addr.

PDI_AXI_ARPROT[2:0]

IN

Read protection type

RD addr.

PDI_AXI_ARVALID

IN

Read address valid

RD addr.

act. high

PDI_AXI_ARREADY

OUT

Read address ready

RD data

act. high

PDI_AXI_RID

[PDI_BUS_ID_WIDTH-1:0]

OUT

Read data ID

RD data

PDI_AXI_RDATA

[PDI_EXT_BUS_WIDTH-1:0]

OUT

Read data

RD data

PDI_AXI_RRESP[1:0]

OUT

Read response

RD data

PDI_AXI_RLAST

OUT

Read data last

RD data

act. high

PDI_AXI_RVALID

OUT

Read data valid

RD data

act. high

PDI_AXI_RREADY

IN

Read data ready

RD data

act. high

PDI_AXI_IRQ_MAIN

OUT

Interrupt

act. high

Please refer to the AMBA AXI and ACE Protocol Specification from ARM

®

for details about the AXI3

bus

.